## Predicting Power and Timing of Large-Scale Distributed Applications on Highly Heterogeneous Platforms

Von der Fakultät für Informatik, Wirtschafts- und Rechtswissenschaften der Carl von Ossietzky Universität Oldenburg zur Erlangung des Grades und Titels eines

Doktors der Ingenieurwissenschaften (Dr.-Ing.)

angenommene Dissertation

von Herrn Jörg Walter geboren am 15. März 1977 in Kiel

**Gutachter:** Prof. Dr.-Ing. Wolfgang Nebel

Weiterer Gutachter: Prof. Dr.-Ing. Axel Hahn

**Tag der Disputation:** 10. Dezember 2020

### Zusammenfassung

Im Bereich des Hoch- und Höchstleistungsrechnens oder auch High Performance Computings (HPC) werden hochgradig parallele Anwendungen auf verteilten Systemen mit hunderten von Rechenknoten ausgeführt. Durch die Dimensionen von Plattformen und Programmen sind Vorhersagen über Laufzeit und Energiebedarf dieser Programme schwierig. Diese Schwierigkeiten werden noch verstärkt, wenn Entwickler ihre Anwendungen optimieren wollen, ohne dazu Messungen durch instrumentierte Probeläufe auf der Zielplattform zu machen. Zudem behandeln die meisten Vorhersagemethoden nur den Zeitaspekt, da bis vor kurzem der Energiebedarf für die meisten HPC-Entwickler keine Bedeutung hatte. Zwei unabhängige Entwicklungen haben diese Situation verändert: Zum einen werden auch bei eingebetteten Systemen immer öfter Cluster-Architekturen eingesetzt, und zum anderen wird im HPC-Bereich inzwischen mit einer Überprovisionierung von Rechenknoten gearbeitet, wodurch ein direkter Einfluss von Energiebedarf auf die verfügbare Rechenleistung entsteht.

Ich stelle in dieser Arbeit einen neuen Ansatz vor, der mit einer Simulationstechnik arbeitet, wie er im Bereich der eingebetteten Systeme verbreitet ist. Will man eine solche Technik auf die Größenordnung von HPC-Systemen anwenden, kann jedoch die eigentliche Anwendungsfunktionalität nicht mehr ausgeführt werden. Stattdessen benutzt die vorgestellte Methodik eine abstrakte Simulation auf Basis von Task-Graphen, wie sie im HPC-Bereich beliebt sind, und die Gemeinsamkeiten mit synchronen Datenflussgraphen aus dem Bereich der eingebetteten Systeme haben.

Vorhersagen zu Rechenoperationen werden über eine messbasierte Charakterisierungsprozedur realisiert. Anders als existierende Trace-basierte Ansätze benötigt diese Prozedur jedoch kein Ausführen der gesamten Applikation auf der gesamten Zielplattform. Es reicht ein einzelner instrumentierter Rechenknoten aus, um die notwendigen Eingabeparameter für die abstrakte Simulation zu generieren. In dieser Arbeit stelle ich auch eine beispielhafte Plattform vor, die zeigt, welche Messdatenerfassung und welche Hardwareeigenschaften die vorgestellte Vorhersagemethodik benötigt.

Während Rechenoperationen abstrakt gehandhabt werden, behandelt die Simulation Kommunikationsvorgänge mit deutlich höherem Detailgrad, da dies mehr Einfluss auf die Genauigkeit der Vorhersagen hat. Das Ergebnis ist eine Vorhersagemethode für Zeit und Energie, die schnell genug für interaktives Feedback bei der Anwendungsentwicklung ist, und die dabei ein hinreichendes Maß an Genauigkeit hat. Dadurch eignet sie sich außerdem für automatisierte Exploration von Entwurfsmöglichkeiten hinsichtlich Algorithmen, Parallelisierungsgrad, oder Task-Granularität.

Ich habe die Arbeit mit Hilfe von direkten physikalischen Messungen evaluiert, anstatt mich nur auf detailliertere Referenzmodelle oder indirekte Messungen wie z.B. Energiemodelle auf Basis von CPU-Ereigniszählern zu verlassen. Dadurch sind unerwartete Effekte sichtbar geworden, die erheblichen Einfluss auf das Systemverhalten haben können. Insgesamt betrachtet konnten die Zeitvorhersagen eine gute Genauigkeit erreichen, die mit etablierten Verfahren vergleichbar ist. Die Evaluation der Energievorhersagen zeigte weniger eindeutige Ergebnisse: Vorhersagen haben ein klares Potential für hinreichende Genauigkeit, aber sie wurden von externen Einflüssen (insbesondere Herstellungsqualität und Umgebungsbedingungen) beeinträchtigt, die im Rahmen dieser Arbeit nicht vollständig kompensiert werden konnten.

### Abstract

Applications in the high-performance computing (HPC) domain are often designed to run on cluster-like distributed platforms with hundreds of nodes. Due to the size of both – applications and platforms – predictions of application run time and energy usage is challenging. Difficulties increase when developers want to guide application design without profiling on a massively parallel platform. Furthermore, most HPC prediction methodologies only address timing, because energy predictions used to have little relevance for HPC application design. Two different developments changed this: Cluster architectures are becoming popular in the embedded domain, and hardware overprovisioning in recent HPC systems creates a direct influence of energy usage on application performance.

I propose a new approach to this challenge based on a simulation technique well known in the embedded computing domain. In order to apply such a methodology at HPC scale, I cannot execute actual applications during simulation. I use abstract simulation based on the Task Graph model of computation, which is popular in HPC and which has properties similar to the synchronous dataflow model that is popular in the embedded domain.

For computation predictions, the methodology uses a measurement-based characterisation procedure. Unlike trace-based HPC prediction methodologies, this procedure does not require a full application execution over the entire target platform. Instead, a single instrumented cluster node is sufficient to create input parameters for the abstract simulation. I present an exemplary embedded cluster that demonstrates the measurement instrumentation and hardware properties required by the proposed methodology.

While the simulation handles execution in an abstract way, it keeps a high level of detail for communication, since this has much bigger impact on overall accuracy. The end result is a time and energy prediction methodology that is fast enough for interactive feedback in the application design workflow while still maintaining a useful level of accuracy. It also allows designers to employ automatic design space exploration across a wide range of high-level design choices like choice of algorithms, degree of parallelism, or task granularity.

I have performed the evaluation of the proposed methodology against direct physical measurements, and not against more detailed reference models or indirect measurements like CPU performance counter based energy models. This has uncovered unexpected practical issues that can have significant impact on system behaviour. Overall, timing predictions can reach a high degree of accuracy, fully on par with established HPC prediction methodologies. The evaluation of energy predictions is less conclusive: results clearly show a potential for useful accuracy, but they have a higher dependency on external factors like hardware build quality and environmental conditions than could be controlled for in this thesis.

### Publications

Some ideas and figures have appeared previously in the following publications:

- [1] J. Walter, R. Görgen, and W. Nebel, "Predicting performance and energy efficiency for large-scale parallel applications on highly heterogeneous platforms," in 19th GI/ITG/GMM Workshop Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen, MBMV 2016, Freiburg im Breisgau, Germany, March 1-2, 2016., 2016, pp. 116–127.

- [2] J. Walter and W. Nebel, "Energy-Aware Mapping and Scheduling of Large-Scale Macro Data-Flow Applications," in 1st International Workshop on Investigating Dataflow in Embedded Computing Architecture, 2015. 9.6.2

- [3] P. Knocke, R. Görgen, J. Walter, D. Helms, and W. Nebel, "Using early power and timing estimations of massively heterogeneous computation platforms to create optimized HPC applications," in *Proceedings of the 12th IEEE International Conference on Embedded and Ubiquitous Computing*, 2014.

- [4] J. Walter, M. Fakih, and K. Grüttner, "Hardware–Based Real–Time Simulation on the Raspberry Pi," in 2nd Workshop on High-performance and Real-time Embedded Systems (HiRES 2014), Jan. 2014. 10.1.4.1

# Contents

| Ι.  | Int                                                      | roduct  | ion                                           | 15 |

|-----|----------------------------------------------------------|---------|-----------------------------------------------|----|

| 1.  | Context and Motivation 1                                 |         |                                               |    |

| 2.  | 2. Scope of Contribution         2.1. Research Questions |         |                                               |    |

| 3.  | Out                                                      | ine     |                                               | 23 |

| II. | Fu                                                       | ndame   | ntals                                         | 25 |

| 4.  | Tim                                                      | ing and | Energy Prediction for HPC Applications        | 27 |

|     | 4.1.                                                     | Hardv   | vare Aspects                                  | 27 |

|     |                                                          | 4.1.1.  | Speed Variation and Synchronisation           | 27 |

|     |                                                          | 4.1.2.  | Current and Future Hardware Architectures     | 28 |

|     |                                                          | 4.1.3.  | HPC Cluster Scale                             | 28 |

|     |                                                          | 4.1.4.  | Energy Considerations                         | 29 |

|     |                                                          | 4.1.5.  | Heat                                          | 30 |

|     |                                                          |         | 4.1.5.1. Thermal Management                   | 30 |

|     |                                                          |         | 4.1.5.2. Observable Effects                   | 31 |

|     |                                                          |         | 4.1.5.3. Modelling                            | 31 |

|     |                                                          | 4.1.6.  | CPU-specific Performance Optimisation         | 31 |

|     | 4.2.                                                     | Softwa  | are Aspects                                   | 33 |

|     |                                                          | 4.2.1.  | HPC Problem Classes                           | 33 |

|     |                                                          | 4.2.2.  | Parallelism and its Limitations               | 34 |

|     |                                                          | 4.2.3.  | Application Patterns                          | 35 |

|     |                                                          |         | 4.2.3.1. Structural Patterns                  | 35 |

|     |                                                          |         | 4.2.3.2. Parallel Algorithm Strategy Patterns | 36 |

|     |                                                          | 4.2.4.  | Scheduling                                    | 36 |

|     |                                                          |         | 4.2.4.1. Dynamic Scheduling                   | 37 |

|     |                                                          |         | 4.2.4.2. Static Scheduling                    | 37 |

|     |                                                          |         | 4.2.4.3. Rescheduling                         | 37 |

|     |                                                          | 4.2.5.  | Resource Modelling                            | 38 |

|     |                                                          | 4.2.6.  | Auxiliary Aspects                             | 39 |

|     |                                                          |         | 4.2.6.1. Data Representation                  | 39 |

|    |           | 4.2.6.2. Data Distribution              | 39              |

|----|-----------|-----------------------------------------|-----------------|

|    |           | 4.2.6.3. Fault Tolerance                | 40              |

|    | 4.3.      | Parallelisation Tools                   | 40              |

|    |           | 4.3.1. Local Parallelism                | 40              |

|    |           | 4.3.2. Communication Middleware         | 41              |

|    |           | 4.3.3. Deployment                       | 42              |

|    | 4.4.      | Common Benchmarks                       | 42              |

|    | 4.5.      | Common Prediction Approaches            | 44              |

|    |           | 4.5.1. Analytical Models                | 44              |

|    |           | 4.5.2. Simulation                       | 45              |

|    |           | 5                                       | 45              |

|    |           | 4.5.4. Trace-Based Simulation           | 46              |

| -  | <b></b> · |                                         | 47              |

| э. |           |                                         | <b>41</b><br>47 |

|    |           |                                         | 47<br>48        |

|    | 5.2.      |                                         | 40<br>48        |

|    |           | 8                                       | 40<br>48        |

|    |           | 1 · · · · · · · · · · · · · · · · · · · | 40<br>48        |

|    |           |                                         | 40<br>48        |

|    |           | I I I I I I I I I I I I I I I I I I I   | 40<br>49        |

|    | 53        |                                         | 49<br>49        |

|    | 5.5.      | 85                                      | 49              |

|    |           | 0                                       | 49<br>50        |

|    |           |                                         | 51              |

|    |           |                                         | 51              |

|    |           | -                                       | 52              |

|    |           |                                         | 52              |

|    |           |                                         | 53              |

|    |           |                                         | 00              |

| 6. |           |                                         | 55              |

|    | 6.1.      | Components of SystemC Models            | 55              |

|    | 6.2.      | Discrete-Event Simulation               | 56              |

|    | 6.3.      | 5                                       | 57              |

|    |           | 6.3.1. Computation                      | 58              |

|    |           | 6.3.2. Communication                    | 59              |

|    | 6.4.      | Time and Energy Traces                  | 59              |

| 7  | The       | is Contributions                        | 61              |

| 1. |           |                                         | <b>61</b>       |

|    |           |                                         | 63              |

|    | ≠.∠.      | Assumptions                             | 00              |

| 8.           | Rela         | ted W            | ork                                   | 67       |

|--------------|--------------|------------------|---------------------------------------|----------|

|              | 8.1.         | Time a           | and Energy Prediction                 | 67       |

|              |              | 8.1.1.           | Execution-Driven Simulation           | 67       |

|              |              | 8.1.2.           | Trace-Based Simulation                | 68       |

|              |              | 8.1.3.           | Abstract Simulation                   | 69       |

|              |              | 8.1.4.           | Analytical Modelling                  | 69       |

|              | 8.2.         |                  | arement Platforms                     | 70       |

|              | 0.2.         | wieuse           |                                       | 10       |

|              |              |                  |                                       |          |

|              | . Mo         | odels a          | and Methodology                       | 71       |

| 9.           | Pow          | er and           | Timing Prediction Methodology         | 73       |

|              |              |                  | Ill Design Flow                       | 73       |

|              | 9.2.         |                  | act Application Model                 | 76       |

|              |              | 9.2.1.           | Task Graph                            | 76       |

|              |              | 9.2.2.           | Application Semantics                 | 79       |

|              |              | 9.2.3.           | Modelling Process                     | 80       |

|              |              | 9.2.4.           | Discussion of Design Decisions        | 81       |

|              | 9.3.         |                  | tion Runtime Model                    | 82       |

|              | <i>J</i> .J. | 9.3.1.           |                                       | 83       |

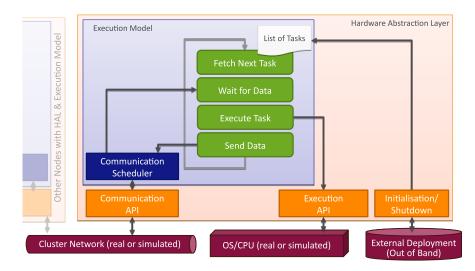

|              |              | 9.3.2.           | Main Loop                             | 84       |

|              |              | 9.3.3.           | Communication Scheduler               | 84       |

|              |              | 9.3.3.<br>9.3.4. |                                       | 85       |

|              |              |                  | Hardware Abstraction Layer            |          |

|              | 0.4          | 9.3.5.           | Overall Design Decision               | 86<br>86 |

|              | 9.4.         |                  |                                       |          |

|              |              | 9.4.1.           | Platform Model                        | 86       |

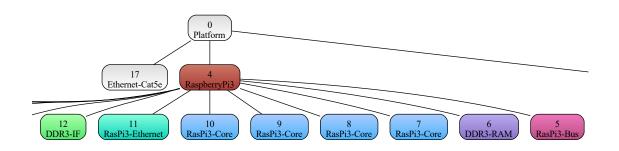

|              |              |                  | 9.4.1.1. Platform Hierarchy Graph     | 86       |

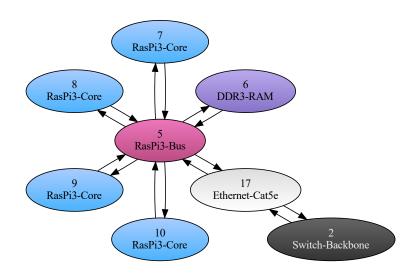

|              |              |                  | 9.4.1.2. Platform Communication Graph | 87       |

|              |              |                  | 9.4.1.3. Platform Graph               | 88       |

|              |              | 9.4.2.           | Platform Resource Model               | 89       |

|              |              | 9.4.3.           | Discussion of Design Decisions        | 89       |

|              | 9.5.         |                  | putation Resource Model               | 92       |

|              |              | 9.5.1.           | Abstract Resource Model               | 93       |

|              |              | 9.5.2.           | Model Building                        | 94       |

|              |              | 9.5.3.           | Discussion of Design Decisions        | 94       |

| 9.6. Mapping |              | Mapp             | ing                                   | 95       |

|              |              | 9.6.1.           | Representation                        | 95       |

|              |              | 9.6.2.           | Automatic Mapping                     | 95       |

|              | 9.7.         | Simula           | ation Model                           | 96       |

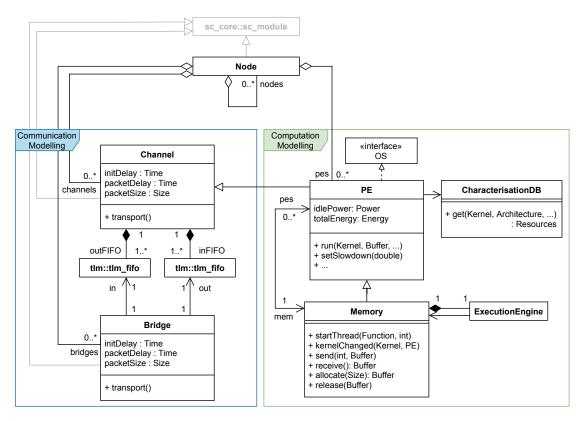

|              |              | 9.7.1.           | SystemC Object Hierarchy              | 96       |

|              |              | 9.7.2.           | Power Models                          | 98       |

|              |              | 9.7.3.           | Computation Modelling                 | 98       |

|              |              | 9.7.4.           | Communication Modelling               | 100      |

|              |              |                  | 9.7.4.1. Basic Operation              | 100      |

Contents

|        |                             | 9.7.4.2.        | Routing                     | . 102 |

|--------|-----------------------------|-----------------|-----------------------------|-------|

|        | 9.7.5. Resulting Prediction |                 |                             | . 102 |

| 9.8.   | Physic                      | sical Execution |                             |       |

|        | 9.8.1.                      |                 | ent                         |       |

|        | 9.8.2.                      | 1 1             | lon                         |       |

|        | 9.8.3.                      | Execution       |                             | . 104 |

|        |                             | 9.8.3.1.        | Node-Local Time             | . 105 |

|        |                             | 9.8.3.2.        | Fime Synchronisation        | . 105 |

|        | 9.8.4.                      | Commun          | ication                     | . 106 |

|        |                             | 9.8.4.1.        | ICP Backend                 | . 106 |

|        |                             | 9.8.4.2.        | Eth Backend                 | . 106 |

| 10 Mea | sureme                      | nt Platfor      | m                           | 111   |

|        |                             |                 | on and Measurement          |       |

| 10.1.  |                             |                 | stribution                  |       |

|        |                             |                 | Front-End                   |       |

|        |                             |                 | quisition                   |       |

|        | 10.1.0.                     |                 | Multiplexer                 |       |

|        |                             |                 | Analog-to-Digital Converter |       |

|        |                             |                 | Data Transfer               |       |

|        | 1014                        |                 | cessing and Transmission    |       |

|        | 10.1.1.                     |                 | Data Reduction              |       |

|        |                             |                 | Transmission                |       |

|        |                             |                 | System Control              |       |

| 10.2   | Embed                       |                 | er Platform                 |       |

|        |                             |                 | lanagement                  |       |

| 10.3.  |                             |                 | DCess                       |       |

|        |                             |                 |                             |       |

|        |                             |                 |                             |       |

|        |                             |                 | relation                    |       |

|        |                             |                 | naracterisation             |       |

|        |                             |                 | Energy Markers              |       |

|        |                             |                 | External Time Measurement   |       |

|        |                             | 10.3.4.3.       | Secondary Time Model        | . 126 |

| 10.4.  | Platfor                     |                 | erisation                   |       |

|        |                             |                 | le Clock Frequency          |       |

|        | 10.4.2.                     | Platform 1      | Power                       | . 127 |

|        | 10.4.3.                     | Commun          | ication Timing              | . 128 |

|        |                             |                 | Cutoff Metric               |       |

|        |                             | 10.4.3.2.       | Model Parameters            | . 129 |

|        |                             | 10.4.3.3.       | Benchmark Suite             | . 129 |

|        | 10.4.4.                     | Commun          | ication Power               | . 130 |

|        |                             |                 |                             |       |

### IV. Evaluation

| 1 | 2   | 1 |

|---|-----|---|

|   | . J | т |

| 11. Evaluation Goals                            | 133 |

|-------------------------------------------------|-----|

| 11.1. Overall Methodology                       | 133 |

| 11.1.1. End User Requirements                   | 133 |

| 11.1.2. Evaluation Criteria                     | 133 |

| 11.1.2.1. Time                                  | 133 |

| 11.1.2.2. Energy                                | 134 |

| 11.1.2.3. Performance                           | 134 |

| 11.2. Measurement Accuracy                      | 135 |

| 11.2.1. Time                                    | 135 |

| 11.2.2. Energy                                  | 136 |

| 11.3. Evaluation Platform                       | 136 |

| 11.3.1. Platform Characterisation               | 137 |

| 11.3.2. Power Variation and Heat                | 137 |

| 11.4. Individual Design Decisions               | 137 |

| 0                                               |     |

| 12. Evaluation of Measurement Accuracy          | 139 |

| 12.1. Setup                                     | 139 |

| 12.1.1. DC Accuracy                             | 139 |

| 12.1.2. Channel Independence                    | 141 |

| 12.1.3. Frequency Response                      | 141 |

| 12.1.4. Time Measurement                        | 141 |

| 12.2. Results                                   | 142 |

| 12.2.1. DC Accuracy                             | 142 |

| 12.2.2. Channel Independence                    | 145 |

| 12.2.3. Frequency Response                      | 145 |

| 12.2.4. Time Measurement                        | 147 |

| 12.3. Discussion                                | 150 |

| 12.3.1. Energy                                  | 150 |

| 12.3.2. Timing                                  | 151 |

| 12.3.3. Summary                                 | 152 |

|                                                 |     |

| 13. Characterisation of the Evaluation Platform | 153 |

| 13.1. Setup                                     | 153 |

| 13.1.1. Platform Model                          | 153 |

| 13.1.2. Platform Characterisation               | 153 |

| 13.2. Results                                   | 154 |

| 13.2.1. Clock Speed                             | 154 |

| 13.2.2. Platform Power                          | 155 |

| 13.2.3. Communication Timing                    | 155 |

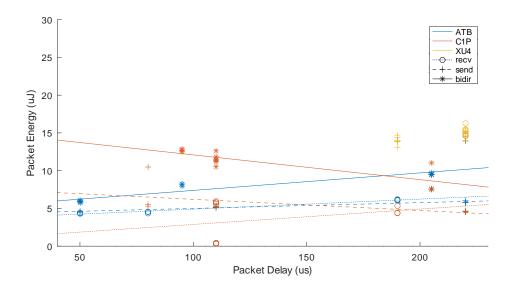

| 13.2.4. Communication Power                     | 159 |

| 13.3. Discussion                                | 159 |

| 13.3.1. Sustainable Clock Speed                 | 159 |

| 13.3.2. Platform Power                         | 162 |  |  |  |  |

|------------------------------------------------|-----|--|--|--|--|

| 13.3.3. Communication Timing                   | 163 |  |  |  |  |

| 13.3.4. Communication Power                    | 163 |  |  |  |  |

| 13.3.5. Summary                                | 164 |  |  |  |  |

|                                                |     |  |  |  |  |

| 14. Evaluation of the Overall Methodology      | 165 |  |  |  |  |

| 14.1. Setup                                    | 165 |  |  |  |  |

| 14.1.1. Overview                               | 165 |  |  |  |  |

| 14.1.2. Measurement Details                    | 165 |  |  |  |  |

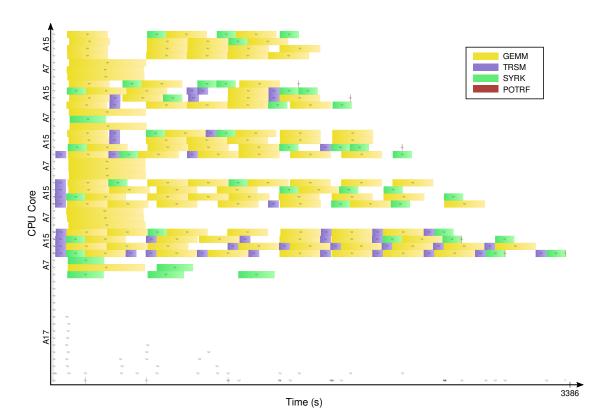

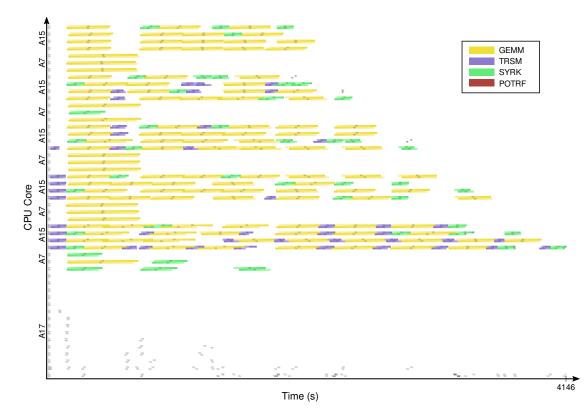

| 14.1.3. Cholesky Matrix Subdivision            | 166 |  |  |  |  |

| 14.1.4. Computation Resource Model             | 167 |  |  |  |  |

| 14.1.5. Application Benchmark                  | 167 |  |  |  |  |

| 14.2. Results and Discussion                   | 168 |  |  |  |  |

| 14.2.1. Computation Resource Model             | 168 |  |  |  |  |

| 14.2.2. Application Benchmark                  | 171 |  |  |  |  |

| 14.2.2.1. Time Predictions $\ldots$            | 173 |  |  |  |  |

| 14.2.2.2. Simulation Speed                     | 173 |  |  |  |  |

| 14.2.2.3. Energy Predictions                   | 175 |  |  |  |  |

| 14.3. Summary                                  | 177 |  |  |  |  |

| 5                                              |     |  |  |  |  |

| 15. Evaluation of Individual Design Decisions  | 181 |  |  |  |  |

| 15.1. Fixed Clock Frequencies                  | 181 |  |  |  |  |

| 15.2. External Time Measurement                | 182 |  |  |  |  |

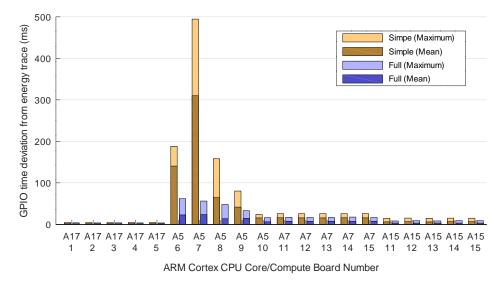

| 15.2.1. Reproduction of Inconsistent Behaviour | 182 |  |  |  |  |

| 15.2.2. Results                                | 182 |  |  |  |  |

| 15.2.3. Discussion                             | 185 |  |  |  |  |

| 15.3. Custom Network Protocol                  | 185 |  |  |  |  |

| 15.4. Custom Runtime System                    | 187 |  |  |  |  |

| 15.4.1. Discussion                             | 187 |  |  |  |  |

|                                                | 107 |  |  |  |  |

|                                                |     |  |  |  |  |

| V. Conclusion                                  | 189 |  |  |  |  |

|                                                |     |  |  |  |  |

|                                                |     |  |  |  |  |

| VI. Appendix                                   | 195 |  |  |  |  |

|                                                |     |  |  |  |  |

| References                                     | 197 |  |  |  |  |

|                                                |     |  |  |  |  |

| List of Figures                                | 203 |  |  |  |  |

|                                                |     |  |  |  |  |

| List of Tables                                 |     |  |  |  |  |

| Listings                                       |     |  |  |  |  |

|                                                |     |  |  |  |  |

| Nomenclature                                   |     |  |  |  |  |

| Nomenclature 209                               |     |  |  |  |  |

# Part I.

# Introduction

### 1. Context and Motivation

In the high-performance computing (HPC) world, platforms have become much more complex over time. Ever since the first Cray supercomputer, a core principle of HPC systems was parallelisation. There is cluster-level parallelism where multiple distinct machines collaborate through explicit communication, and local parallelism where multiple processors within one machine collaborate through shared memory.

The logical continuation of this principle led to clusters of HPC servers, each equipped with multiple processors, each of which as multiple CPU cores. In these clusters, every computation resource (i. e. CPU core) is the same – this is the age of homogeneous supercomputing, which has become rare in the HPC field.

A real change came about when graphics processing units (GPUs) evolved from fixed geometry manipulation circuits to highly parallel single-instruction-multiple-data (SIMD) processors. CPUs had SIMD capabilities as well, but GPUs exceeded the parallelism of CPUs by an order of magnitude or two. People started to use them for scientific computing tasks, and GPUs optimised for this use case are called general purpose GPUs (GPGPUs).

Thus was the concept of heterogeneous supercomputing born. The Top 500 list of the fastest computers on earth is dominated by such machines that consist of clusters of machines, each with multiple multi-core CPUs and multiple GPGPUs.

In order to increase the performance for certain workloads, companies invented various even more unconventional computation resources. Manycore processors like the Intel Xeon Phi or the Adapteva Epiphany tried to bridge the gap between highly parallel but inflexible GPGPUs and versatile but less parallel CPUs. These had impressive capabilities in theory, but were difficult to program, which led to their ultimate demise.

Field-programmable gate arrays (FPGAs) are another unconventional computation resource – programmable logic circuits. Hardware programming has always been challenging to normal software developers. Vendors tried to offer high level synthesis (HLS), i. e. the translation of imperative program code into a hardware description; for many years, this generated inefficient hardware designs. Over time the situation has improved: HLS is now capable of delivering competitive designs, but programmers still need high familiarity with the strengths and weaknesses of programmable logic.

The most important development towards accessibility of FPGAs to normal programmers was the combination of traditional CPU cores and FPGA fabric on a single chip. This made it easy to accelerate those parts of a program that would profit the most, while everything else could be written in a traditional programming language. Essentially, people now use FPGAs as add-on accelerators like GPGPUs. As an example for their success, big cloud providers now offer all three types of computation resources (CPUs, GPGPUs, FPGAs) for rent.

#### 1. Context and Motivation

What keeps FPGAs from becoming a mainstream accessory is complexity: HPC programmers have adapted to CPU+GPGPU programming, but they already need two fundamentally different mental models for them. Even assuming that HLS works perfectly, a third type of computation element massively increases the amount of possible hardware setups and parallelisation strategies. HPC needs new ways to manage complexity. How do you optimise programs for such systems? How do you design efficient hardware platforms?

Another emerging challenge is energy usage of HPC systems. The 'Green 500' list is a companion to the Top 500 list of supercomputers that lists the most energy-efficient machines on earth. Yet users of shared HPC systems have no energy constraints whatsoever. They apply for computation time, get assigned a time slot, and can do whatever they want during that time. All this despite the fact that power supply leads to many follow-up costs: there is the cost of energy itself, there is the cost of cooling systems, and finally there is the cost of power distribution, which is massively overprovisioned in order to cope with the worst case, even though that is so rare that it may never occur during the lifetime of the cluster.

On the other hand, there are no established methodologies for programmers to consider energy usage of their programs. They want to optimise their programs *before* running them on the HPC system, but how do you find out if your program will stay within a desired energy limit?

Meanwhile, a research field on the opposite end of the 'hardware size' scale answers all these questions on a daily basis: Embedded system design, more specifically electronic system-level design, deals with exactly these questions: Given an abstract description of some functionality and constraints on timing and energy usage of that functionality, how do you build a system that performs this functionality within those constraints? How do you optimise such a system to minimise some arbitrary cost function? How do you decide which parts to implement in hardware or in software? What computation resources do you need? How do they communicate?

### 2. Scope of Contribution

In this thesis, I try to answer the emerging questions from the HPC field with lessons learned while answering the same questions in the embedded field. I propose a methodology that allows users to model software applications and hardware systems, to map applications to systems, and to get a prediction for time and energy of the resulting execution. The massive difference in system and application size requires trade-offs that would be unforgivable in embedded systems, but are inevitable for HPC applications.

One scenario I had in mind while developing the methodology is the process of design space exploration (DSE). In embedded system design, it is an established way to explore many different system configurations in order to find the set of Pareto-efficient solutions.

Thus my secondary goal is that the proposed prediction methodology is fast enough so that users can perform semi-automatic DSE over many design choices: Choice of fundamental algorithms, granularity of parallelisation, or usage of and mapping to computation resources. Commercial HPC users might want use predictions to design a hardware platform that is cost-optimised for a specific, known set of applications.

I consider this thesis a first step: It does not yet handle the full heterogeneity described above, but the methodology I present is intentionally generic and extensible so that future work can expand on it.

### 2.1. Research Questions

The resulting research questions I want to answer are these:

**Research Question 1.** How can programmers of HPC applications manage the complex design space of different algorithms, possible target platforms, and mappings of their applications onto a platform?

This an overarching question which the following questions derive from. It addresses the increased complexity of the modern HPC landscape. A systematic methodology is a common strategy for complexity management. For embedded systems, model-based design methodologies are well established. High performance computing does not yet have as much acceptance for more formal ways of designing applications.

**Research Question 2.** *How can programmers model applications so that their fundamental structure becomes more accessible to automated tools and formal methodologies?*

When trying to formalise a design methodology, especially when introducing automated processing steps, the source application should make it easy to extract the required

#### 2. Scope of Contribution

information. Just like assembler code is difficult to translate into a high-level programming language, arbitrary C++ code does not readily show opportunities for parallelisation or optimisation.

**Research Question 3.** *How can programmers model the platform they are targeting in an abstract way?*

For the same reason, such a design methodology also needs information about available computation or communication resources and key properties like computation speed or communication bandwidth.

On the other hand, many hardware details are not accessible to users of the hardware. Therefore it would be pointless to model every microarchitectural detail of a system. The model must support a granularity that matches observable metrics.

As a bonus, having an abstract model also enables users to model hypothetical platforms and explore the impact of a different target system.

# **Research Question 4.** *How should an application behave when executed on the modelled hardware?*

Having an application model does not mean that its execution behaviour is fully specified. Programmers probably don't want to create a full semantic specification for themselves; it is sufficient that the methodology includes a specific runtime behaviour that is reasonably efficient.

This execution model is also required for the following group of questions, because predictions can only work if execution behaviour is sufficiently specified.

## **Research Question 5.** *How can programmers of HPC applications optimise them without running them on the intended target platform?*

This is the second fundamental question that guides more detailed research questions. It is based on the observation that HPC platforms are often not accessible to programmers while they create the bulk of their applications. In the embedded field, hardware/software co-design poses a similar challenge: How do you test software written for hardware that does not yet exist? A common answer is 'simulation', and this thesis expands on this insight.

# **Research Question 6.** *How can a simulation predict timing and energy of an application running on a target platform without executing functional behaviour?*

This is the key challenge when trying to simulate HPC applications on a typical development system: how to get it fast. The faster predictions can be generated, the better will the methodology be accepted by programmers for daily use. Indirectly this also addresses the question of making simulation fast enough for design space exploration.

Executing real HPC code on a developer workstation would already be much too slow outside of a simulator. If no functional behaviour can be executed, then the simulation needs a different way to determine time and energy; this question asks for some other resource usage model. **Research Question 7.** *How can programmers create an abstract resource model when they don't have access to the target platform?*

This assumes that programmers cannot simply go to the target machine, hook up a multimeter, execute their program, and measure energy. The resource model should be designed in a way that developers can create missing parts of the resource model using tools that fit on their desks and in their budgets.

# **Research Question 8.** *How do you measure energy and timing for the abstract resource model properly?*

Going further into details, it is surprisingly complex to acquire good measurement data. This is not about the general question of how to measure correctly, which should be part of basic technical education. This is about the question which aspects are important for the proposed methodology. Ideally, a recommended best practice shows a systematic way of performing relevant measurements. 2. Scope of Contribution

## 3. Outline

This thesis is structured in five parts.

**Part I - Introduction** gives a general overview of the topic of this thesis. It concludes with this outline.

**Part II - Fundamentals** contains five subsections covering relevant topics from the technological environment this thesis is based on.

Section 4 covers topics that relate to HPC hard- and software, execution behaviour, and existing time prediction approaches; it also covers energy, but there is little work that specifically relates to HPC applications – this is a very recent field of research.

Instead, this is covered more generically in Section 5, which addresses the practical side of measurement of time and energy of hardware that is running applications.

After that, Section 6 deals with the simulation side of things, specifically SystemC as a discrete-event simulation framework.

After all related technologies have been presented, Section 7 states the specific contributions that this thesis makes; The part concludes with an overview of related work in Section 8.

**Part III - Models and Methodology** introduces the overall methodology. Section 9 presents the proposed overall design flow and all of its components, many directly addressing the research questions.

Section 10 then presents the evaluation platform I have built for this thesis. While part of the platform only exists for evaluation of the proposed methodology, the actual measurement infrastructure is a more generic proposal for creation of the resource model. Furthermore, the section also proposes a systematic approach to create a specific model and to check platforms for some effects that would impair usage with the proposed methodology.

**Part IV** - **Evaluation** then presents the evaluation process and its results. In Section 11, I present four evaluation goals, give an overview of each and derive detailed evaluation criteria. I then describe the evaluation process for each of the goals in Section 12 through Section 15, where Section 14 evaluates the main contributions.

**Part V** - **Conclusion** sums up the results of this thesis and presents promising extensions for future work.

3. Outline

# Part II.

# **Fundamentals**

## 4. Timing and Energy Prediction for HPC Applications

In the field of high performance computing (HPC), applications and platforms are much larger than in virtually any other computing domain. This poses unique challenges for attempts to predict execution times of programs.

Most importantly, the platforms being predicted are orders of magnitude bigger than the platforms used for development. Moreover, they often use specialised hardware and specialised application modelling approaches. The latter two properties also apply to embedded systems engineering, which is why the methodology proposed in this thesis actually has its roots in the embedded domain.

### 4.1. Hardware Aspects

Apart from the size, HPC hardware has another significant difference to embedded systems: Embedded systems usually run tightly synchronised, up to the point that different compute resources run off a single master clock signal. In contrast, HPC systems are built as an asynchronous cluster architecture.

A typical HPC cluster – as assumed for this thesis – consists of multiple compute nodes. A compute node is a computer that has one or more performance-optimised multi-core CPUs and possibly specialised compute accelerators. It is equipped with main memory (RAM) that is directly accessible to all compute resources in that node. That memory might have different timing characteristics depending on which computing resource wants to access which address (nonuniform memory architecture, NUMA).

Nodes are connected through a high-bandwidth networking technology, often Ethernet or InfiniBand, and the topology of this network need not be a simple star topology, e.g. it might be hierarchically structured.

Due to the distributed nature, and due to the size of applications and data sets, internode communication is a critical resource. Foreign traffic can have significant impact on application performance, so the cluster network is mostly isolated from the outside world, often only offering a single gateway node that manages application and data deployment.

#### 4.1.1. Speed Variation and Synchronisation

With regard to this thesis, the most important implication of this architecture is the fact that different parts of the system run completely asynchronously. Clock speeds vary

#### 4. Timing and Energy Prediction for HPC Applications

due to manufacturing variations. Their speed even changes over time due to thermal effects. And nodes usually do not know their exact speed in relation to other nodes.

The employed networking technology does not offer a real-time mode of operation<sup>1</sup>; it works asynchronously, usually employing a store-and-forward approach for routing network packages.

Thus, time based synchronisation only works in the millisecond range, e.g. through the Network Time Protocol (NTP) [39]. Event based synchronisation needs to happen on higher levels of the communication protocol stack.

The net result is that events happening on different nodes cannot easily be synchronised, and event sequences from different nodes are difficult to relate to each other. It also means that applications that need frequent global synchronisation pay a significant performance overhead, which has implications for the suitability of different models of computation.

#### 4.1.2. Current and Future Hardware Architectures

Current HPC systems have a slight degree of heterogeneity. Nodes tend to be identical. They usually consist of one or more high performance x86 CPUs and one or more general purpose GPUs (GPGPUs) as accelerators.

Some problems benefit from a higher count of slower CPU cores. For these applications, ARM based servers exploit the power saving nature of current ARM CPUs to densely pack many ARM CPUs in a small form factor, improving computation density.

GPUs are popular accelerators specialised for numerical computation. They are highly parallel floating point arithmetic units that can process thousands of (homogeneous) calculations in parallel. On such tasks, they usually exceed CPUs in performance per Watt or performance per cost. But for some problems, Field Programmable Gate Arrays (FPGAs) achieve higher efficiency than GPUs (e. g. [40]), so they start to appear in HPC systems as well.

Finally, there are approaches that allow combination of these elements in a single server rack mount [14]. With these HPC systems, users can build their hardware to solve the problem at hand in the most efficient way (by whatever efficiency metric they choose).

#### 4.1.3. HPC Cluster Scale

HPC systems exist in various sizes. Smaller ones are used in commercial applications. For example, many engineering domains use a finite elements approach to physics simulations. These divide a physical volume of the real world into millions of sub-volumes and predict the interaction of physical properties (gas pressure, liquid flows, forces, etc.) for each of them. Another application of highly parallel commercial computation is video processing (encoding/transcoding, rendering of computer generated imagery,

<sup>&</sup>lt;sup>1</sup>There is Ethernet Time Sensitive Networking (TSN), but it is not commonly used in HPC.

image analysis). Finally, machine learning is an emerging high-performance problem that also has applications in the embedded domain.

These systems may be as small as a single cluster node (making it just a regular computer) or as big as a few 19" server racks, resulting in tens or hundreds of nodes, typically with a power consumption below 1 MW [24].

The other notable application is research, where the biggest HPC systems are used [11]. These consist of thousands of nodes and typically consume up to 16 MW [24]; even 20 MW is acceptable for future systems [23].

#### 4.1.4. Energy Considerations

In research HPC systems, actual end users usually don't need not take energy into consideration, because resource allocation is solely based on time. In contrast, the operators do care about energy. First of all, power limits the size of HPC systems as power distribution is far from trivial [23]. Secondly, power translates into operating costs.

In special-purpose HPC systems as found in commercial settings, the set of applications is limited and possibly even known ahead-of-time. Since end users and operators are much closer, an energy-aware development methodology like the one presented in this thesis might be beneficial: Energy usage of applications directly relates to the profitability of the commercial activity. Additionally, predicting energy usage prior to building the HPC system can lead to significant cost reductions by using an optimised hardware setup.

In fact, this approach is also actively researched in the scientific HPC community, just from a slightly different angle.

First of all, there is simple reduction of operating costs by trying to reduce power of unmodified applications. Dynamic voltage/frequency scaling (DVFS) is a way to reduce power which usually comes at the expense of performance. A smart scheduler (see Section 4.2.4) can avoid this. For example, the SuperMUC-NG HPC system already employs an energy-aware DVFS scheduler that uses performance predictions to save energy without performance impact [22].

A different approach is hardware overprovisioning: Traditional HPC cluster design is usually power overprovisioned, i. e. much of its power distribution capacity is never used in real-world applications. The ratio between average operating power and provisioned worst-case power can be as bad as 60 % in real world clusters, yet there are rare workloads (HPC LINPACK, see Section 4.4) that exploit the worst-case limit [49]. Running at 60% peak power also means that cooling systems and power converters run at less efficient operating points.

In contrast, a hardware overprovisioned cluster has more compute nodes than its power distribution system can power simultaneously. It can then dynamically use as many nodes as the power limit allows, which leads to efficient operation for cooling and power distribution. Since cooling and power distribution are expensive for Megawatt class clusters, this can be economically beneficial [50] while also improving overall performance [49].

#### 4. Timing and Energy Prediction for HPC Applications

Such a hardware platform effectively is a dynamically reconfigurable one. Cluster management software must decide which nodes to use for a given workload – which is a classic allocation optimisation problem. It could be addressed by a prediction-based design space exploration workflow like proposed in this thesis. In fact, existing management software does exactly that, just with massively simplified prediction models. For example, the RMAP resource manager [48] uses a set of instrumented executions in various configurations to build a linear regression model which predict all other configurations.

#### 4.1.5. Heat

All electronic circuits convert the largest part of their supply power into heat. This power can be separated into static and dynamic parts, where dynamic power leakage scales linearly with clock frequency. If heat rises too high, CPUs suffer transient failures or even permanent damage.

While changes in energy consumption can happen in almost arbitrarily short time spans, heat distribution and dissipation is a comparably inert effect. This means that overall temperature depends on the average power over a certain time span; with realworld materials, it is inherently low-pass filtered.

#### 4.1.5.1. Thermal Management

Modern performance-oriented CPUs support clock frequencies that would cause heat failure when used permanently. They assume that the workload is mixed and contains enough idle time so that overall heat production stays within the safe operating range.

The limitations of heat dissipation are so prevalent that modern CPUs don't even advertise their maximum clock speed as nominal clock speed. They can no longer guarantee continuous operation under their maximum clock frequency. Instead they specify a safer, slower speed, and call the ability to exceed this clock depending on circumstances by various marketing terms (e.g. Precision Boost for AMD and Turbo Boost for Intel). CPU vendors for mobile devices sometimes use a different approach and specify a maximum duration for the nominal clock speed. CPUs might also switch to lower than nominal clock speeds if heat rises too high.

Another approach to manage heat is to completely shut off parts of an integrated circuit. Parts of circuits that cannot be powered due to heat or energy constraints are also known as *dark silicon*. Some CPUs temporarily (and repeatedly) suspend the entire chip in order to prevent dangerous heat levels; this is also known as *thermal throttling*.

Finally, CPUs may contain a last-resort protection mechanism that turns the CPU off or resets it if – after employing all previously mentioned mechanisms – temperature still rises to a damaging level.

#### 4.1.5.2. Observable Effects

The net effect is that practically achievable CPU performance depends on the amount of cooling. More efficient cooling means that the CPU spends less time throttling, or at a higher clock frequency.

Another effect of heat is that it affects energy consumption. For metal-oxide semiconductor field effect transistors (MOSFETs) as used inside virtually all digital circuits these days, heat increases their so-called subthreshold power leakage, leading to increased static energy consumption.

Furthermore, real-world electronic components have a nonzero temperature coefficient: their internal resistance changes with temperature. The temperature coefficient of silicon-based components is a complex topic, but most other components always have a positive temperature coefficient, i. e. their resistance increases with heat. For example, if the overall resistance of voltage converter components increases, conversion efficiency drops, and this directly affects overall power consumption. Even the copper PCB traces, which inevitably heat up through heat dissipation from the CPU, will add to the losses.

These effects are big enough that there is a significant overall effect on modern electronic circuits that is easy to observe through measurements.

#### 4.1.5.3. Modelling

Unfortunately, accurate heat modelling requires deep insight into the physical structure of the CPU (see [46] for an example), which is not available for off-the-shelf hardware.

As a substitute, heat effects can be accounted for through controlled circumstances. Heat dissipation from a hot into a cool material is proportional to their temperature difference. Thermal coefficients on the other hand are constant<sup>2</sup>. At some point, a circuit with positive thermal coefficient will reach thermal equilibrium, i. e. a balance between heat generation and dissipation. Under the assumption that dynamic power behaviour doesn't significantly change the thermal equilibrium, modelling can then pretend that there are not thermal effects.

This has the potential to interact in complex ways with the active thermal management mechanism presented above. Clock frequency scaling should behave mostly predictable once thermal equilibrium is reached. However, the more extreme protection mechanisms (throttling, reset) have the potential to disrupt predictability due to their blunt nature. These should be avoided if predictability (or performance, or stability, for that matter) is desired.

#### 4.1.6. CPU-specific Performance Optimisation

Most CPUs include complex techniques to speed up execution. While CPU clock frequency should have direct influence on application performance, bottlenecks of the memory subsystem may lead to CPU cycles spent on waiting for data, for example.

<sup>&</sup>lt;sup>2</sup>At least within a few 10 K around room temperature. Universally speaking, they are not constant at all, and MOSFETs are special as well, but that doesn't matter here.

#### 4. Timing and Energy Prediction for HPC Applications

With desktop applications, users take these optimisations as they are and simply buy a faster computer if performance is insufficient. If you're working with one of the fastest computers that exist, that is not an easy option<sup>3</sup>. Thus, authors of HPC software usually invest much time in optimising algorithms for these effects, despite the fact that most of the optimisations are time consuming and highly CPU-specific.

Some of these effects are:

- **Caching** Caches keep frequently used memory content in a fast temporary memory area. To profit from this, applications need cache friendly data arrangement. This is one of the most important small scale optimisations in HPC, and one of the most generic ones.

- **Prefetching** If applications know in advance what data they need, they can instruct the CPU to fetch that data early enough so that memory latency is partially or completely hidden. This optimisation usually depends on specifics of CPU and/or cache architecture.

- **Out-of-order execution** The CPU itself might be able to rearrange instructions so that operations that wait for data are set aside. It can then execute instructions that have no unfulfilled data dependencies instead. This is typically not accessible to manual optimisation.

- **Multiple issue** Some CPUs can even execute multiple instructions at the same time, as long as they don't use the same internal resources (FPU, ALU, etc.). Again, this is almost impossible to optimise for.

- Speculative execution When there is no better alternative, CPUs might execute instructions speculatively, i. e. without knowing the data they are dependent on. They simply guess, and if the guess is correct, speed is gained. Otherwise, CPU state is reverted without any loss<sup>4</sup>. To optimise for this technique, developers can arrange branches so that the most likely outcome is the one guessed by the CPU.

- **Simultaneous Multi-Threading (SMT)** With SMT, the CPU provides multiple logical CPU cores that share the resources of a single physical core. By executing multiple independent threads tightly interleaved, out-of-order execution and multiple issue optimisations become more effective as the CPU can choose between completely independent instruction streams. Effectively, this is makes multiple issue hardware visible through the threading API.

- **Write reordering** Not just instructions can be reordered. Writes to memory can also benefit from reordering and combining. This is less of an optimisation target and more of a performance impediment to watch out for; it slows down synchronisation between threads. Reordered writes may not become globally visible in the

<sup>&</sup>lt;sup>3</sup>Just like the embedded domain, but for a totally different reason: upgrading hardware is easy, but cost per unit matters a lot when producing millions of embedded control units.

<sup>&</sup>lt;sup>4</sup>For the purpose of this thesis, the Spectre and Meltdown class of security vulnerabilities are not relevant. Mitigating them does incur a measurable performance impact.

order they appear in the program, so extra effort must be spent for safe thread synchronisation.

As an overall measure of the availability and effectiveness of these optimisations, the IPC metric (instructions per cycle) describes typical throughput of a CPU.

The methodology proposed in this thesis assumes that task granularity is so large that these effects are not relevant to overall application modelling. However, Section 9.5 shows a simple way to account for the effect of sharing common resources between tasks (cache, SMT).

### 4.2. Software Aspects

Due to developments in the space of HPC hardware, awareness for energy aspects is increasing. Nevertheless, the usual goal during development of HPC applications is to minimise their overall execution time (called *makespan*), since the result is what the user of an application is interested in most. This is a hard enough problem by itself.

Since HPC platforms these days are highly parallel platforms, one of the most important high-level optimisation challenges is to overcome parallelisation limits inherent in algorithms in general or implementations in particular. And since most HPC problems belong to one of a few generic classes of algorithms, there are also generic strategies to address these challenges. The following subsections give an overview of existing concepts that are related to the methodology proposed in this thesis.

#### 4.2.1. HPC Problem Classes

In order to discuss HPC application optimisation, it is useful to classify them. Many problems have a natural formulation in one of a number of computational patterns (as defined in [12]). Notable problem classes are:

- **State Space Exploration** Many problems require searching a state space for a state that either fulfils some condition or that optimises a criterion (often called *cost function*). Various search strategies exist, either exact methods (backtracking branch and bound, dynamic programming) or probabilistic heuristics (simulated annealing, genetic algorithms, ant colony optimisation).

- **Linear Algebra** Problems that require linear algebra to solve, often revolving around matrix multiplications. This is one of the largest classes of problems; many real-world problems can be reduced to linear algebra, e.g. artificial neural networks. Subclasses are dense and sparse linear algebra, where sparse problems take advantage of the fact that their matrices have many zero elements, eliminating a significant amount of computation.

- **Mesh** Problems that model a system as a mesh of discrete points or volumes. Each mesh node's behaviour depends on its neighbourhood. This is another huge class of

problems, as finite element physics simulations fall into this category. Meshes can be structured (tightly coupled to the geometry they model) or unstructured. Structured meshes can exploit the regularity of their structure to optimise calculations, while unstructured meshes allow higher resolution in areas of interest without forcing the whole mesh to have that high resolution, effectively reducing data size.

**N-Body** Problems consisting of a system of N members where the behaviour of each member depends on all other members, not just its neighbours. Naïve solutions have a time complexity of  $O(N^2)$ , which requires approximation schemes for large N. For example, physics simulations that consider long range interactions (like gravity or electromagnetic fields) fall into this category.

This thesis is not restricted to a single problem class, but evaluation is heavily based on linear algebra (see Section 14.2.2).

#### 4.2.2. Parallelism and its Limitations

Since the possible speed of a single CPU is limited by available technology, using many CPUs in parallel is the only way to speed up software further. Of course, applications must be written in a way that allows distribution across multiple CPUs. Due to various effects, application speed does not scale linearly with the number of CPUs.

Most obviously, theoretically achievable speedup depends on the relative amount of work that can be parallelised. Amdahl's Law [16] describes this in a generic way.

Communication is another important aspect that can significantly limit achievable speedup. Assume two processing steps *A* and *B*, where *B* processes data that *A* generates. If they run on different cluster nodes, communication increases the latency of the combined processing sequence. This can slow down maketime directly.

This does not exclusively apply to inter-node communication. Node-local communication can result in memory copies and cache pollution, adding measurable latency as well.

The distributed case, however, allows an easy improvement: Interleave multiple processing sequences so that some independent computation C is performed while B waits for data. This is sometimes called *communication hiding* and is an important optimisation for distributed computing.

If there is no other computation that the node of *B* can perform during communication, computing resources go unused and the actually achieved parallelisation is less than the theoretical maximum. *Utilisation* expresses this as the ratio of used over available computing resources.

Some problems are very prone to such effects. For example, mesh and N-body problems need bidirectional exchange between elements after every simulation time step. This tight coupling makes communication hiding difficult. More generally speaking, any kind of global synchronisation has the potential to severely limit utilisation.

As a result, communication patterns are an important optimisation target. For regularly structured problems on mostly homogeneous hardware, efficient communication strategies are easy to implement using established HPC middleware like Message Passing Interface (MPI). On platforms with higher degrees of heterogeneity or with less regularly structured problems, maximising utilisation is difficult<sup>5</sup>.

In fact, communication in such complex situations is a major aspect of the methodology proposed in this thesis.

#### 4.2.3. Application Patterns

Scheduling parallel systems is a varied, well established research field [53]. To make matters more complex, application design influences which scheduling algorithms are even applicable. For example, dynamic task parallelism cannot be scheduled ahead-of-time.

Therefore it is useful to classify parallel applications through design patterns. From the classification in [12], some notable patterns for HPC problems are structural and parallel algorithm strategy patterns.

#### 4.2.3.1. Structural Patterns

describe high level software architecture, mainly concerning data flow and only to a lesser extent control flow. Examples are:

- **Pipe/Filter** Streaming data is processed by filters (computation) that are connected by pipes (communication). Filters are assumed to be stateless, which makes the whole setup easily parallelisable.

- **Map/Reduce** Independent data sets are first transformed individually in a *map* operation, then summarised in a *reduce* operation. Due to the independence of the data sets, he *map* step is easy to parallelise, while the *reduce* step may or may not be parallelisable. The latter often uses a binary partitioning approach.

- **Iterative Refinement** A data set represents some initial state. The program is repeatedly applied to the data, creating an increasingly accurate approximation of the desired solution. Iteration stops when some terminating condition is met.

In the case of mesh and N-body problems, iterations usually represent time steps, and the terminating condition is either a desired time span or the detection of a stable state.

**Arbitrary Task Graph** This is a generalisation of the other design patterns. The task graph expresses how different parts of the application (the *tasks*) interact with each other. There are many variants; some are pure data flow graphs (like used in this thesis, see Section 9.2.1), some are control flow graphs, or a combination of these, e. g. [10]. Likewise, there are various semantics for tasks.

<sup>&</sup>lt;sup>5</sup>Probably an NP-hard problem, although the claim is too vague for a definite proof.

#### 4.2.3.2. Parallel Algorithm Strategy Patterns

describe how the parallelisation of a software architecture is organised. As a result, these patterns have a high impact on how work can be distributed and scheduled across a cluster. Examples are:

**Task Parallelism** The algorithm is decomposed into a collection of *tasks*, and dependencies between tasks are known. Except for these dependencies, execution order is unspecified and does not affect the final result. If tasks are completely independent, the pattern is also known as *embarrassingly parallel*.

Task parallelism can be static or dynamic. In the dynamic case, running tasks spawn new tasks on demand, while otherwise the set of tasks is known in advance. Dynamic task parallelism is especially suitable for dynamic programming problems.

- **Pipeline** This is a specialisation of task parallelism: a sequence of dependent tasks executes on an independent set of data elements. While a single data element needs to visit each task in sequence, each task can work on a different data element at the same time. Stream data processing (audio/video) often uses a pipeline architecture. If task execution times are data independent, scheduling a pipeline is much easier than scheduling generic task parallelism.

- **Data Parallelism** With this pattern, the same operation is applied to multiple data sets at the same time. This is most useful for node-local parallelisation using CPU vector instructions (SIMD single instruction multiple data), which process a fixed number of data streams in parallel. This is also a useful pattern for GPGPU acceleration.

In the distributed case, data parallelism mostly results in an embarrassingly parallel problem. There are exceptions: The reduction step of the Map/Reduce structural pattern also counts as data parallelism but isn't embarrassingly parallel.

**Discrete Event** This pattern is based on a collection of tasks that interact in unpredictable (or at least highly irregular) intervals. It is popular in the embedded domain as a simulation technique for intrinsically parallel hardware [7], and in modern industry automation [5]. It is uncommon in HPC because it needs frequent synchronisation between cluster nodes, which reduces performance significantly (see above).

In this thesis, the focus lies on task parallel programs expressed as static task graphs (see Section 9.2.1).

#### 4.2.4. Scheduling

Static task graphs are a fairly generic model of computation that allow a wide variety of execution strategies. Furthermore, both dynamic (event driven) and static scheduling approaches apply.

In [53], the authors developed a detailed taxonomy of scheduling algorithms. In the area of modern high performance computing, a few classes are notable:

#### 4.2.4.1. Dynamic Scheduling

Dynamic scheduling in a cluster is more or less equivalent to load balancing when applied to embarrassingly parallel problems on homogeneous platforms. Since there are no dependencies between tasks, overall execution speed is merely a matter of keeping execution units busy. Dynamic scheduling can be *centralised* (doesn't scale well; e. g. [41]), *hierarchical* (scales better, but has problems beyond 10000 cores; e. g.[42]), or fully *distributed*.

The most popular fully distributed dynamic parallel scheduling method is *work stealing* [54], which has evolved into an entire class of schedulers. It works by managing local queues of tasks to execute. If an execution unit is idle it will execute the next task from the local task queue. If the queue is empty the node will remove a task from a random other node's task queue and add it to its own queue. Work stealing provides upper bounds in space and time that are within a constant factor of optimum values [55]. It has been shown that it also scales well in practice [61].

The complementary class to work stealing is called *work sharing*. In this class, local or global schedulers push tasks out to execution units instead of execution units pulling tasks. Centralised and hierarchical schedulers are usually work sharing, although it is possible to implement work stealing on top of a hierarchical structure [56].

#### 4.2.4.2. Static Scheduling

Besides fully dynamic scheduling there is static scheduling. There, all cluster nodes have a list of tasks to execute, and possibly also a time when to execute them. The latter part is common in embedded time triggered architectures. Due to the synchronisation difficulties in large cluster architectures, they usually use some kind of dependency management instead of fixed execution times, i. e. tasks start as soon as their dependencies are fulfilled.

While dynamic scheduling usually doesn't even know the exact workload, static schedulers can reason about the entire application and thus (in theory) can calculate an optimal schedule. For the general case this is an NP-hard problem, however, so a multitude of approximations and heuristics exist.

Furthermore, schedule quality depends on the resource model used for predicting execution and communication time. On the other hand, schedules can easily take into account other metrics like energy (as done in this thesis), as this does not change the fundamental nature of the optimisation problem, only its size.

#### 4.2.4.3. Rescheduling

Finally, there is the approach of periodic rescheduling as a way to make static schedulers able to react to changes in applications or platforms. It uses a static scheduler that is

#### 4. Timing and Energy Prediction for HPC Applications

invoked in response to some event (application changes, platform changes, or simply at regular intervals).

This allows a static scheduler to reevaluate its choices to compensate for unpredictable developments during execution. Most importantly, it allows compensating for incorrect timing predictions due to insufficient resource models.

The main problem with this approach is of course the processing time the scheduler needs. If the scheduler needs more resources than an updated schedule can save, its execution is pointless. If the latency of the scheduler results in long idle times for execution units, its execution is actively detrimental. Also, publishing a new schedule needs some kind of synchronisation, which further hurts performance.

This thesis assumes a fully static scheduler and proposes an improved scheduler with O(n) time complexity as a secondary contribution (see Section 9.6). Rescheduling could be introduced in the future.

#### 4.2.5. Resource Modelling

All task schedulers have in common that they need some kind of model that assigns a cost to each decision. For dynamic schedulers, this is often as simple as a bimodal model where idle processing units have high costs and busy ones have low costs assigned; there is no distinction made between different tasks. In other words, they use utilisation as their main metric. Unused processing capacity is avoided under the assumption that this will optimise application makespan.

Since dynamic schedulers react on observed task performance, this assumption works well, as shown in [55].

This is not generally true for heterogeneous platforms. For example, an idling general purpose processing unit may better be left idling if a suitable highly efficient unit will become idle within a short time span. Furthermore, optimising for other metrics than makespan is difficult. This is where static schedulers have an advantage.

As mentioned before, static schedulers can exploit more detailed resource models, but creating them is difficult. On smaller platforms, various approaches work: register transfer level (RTL) simulations, analytical models provided by CPU manufacturers, or plain measurements. However, HPC platforms usually don't have enough idle time for measurements (assuming they even have measurement infrastructure), don't come with manufacturer-supplied models, and use CPUs that are too complex for RTL simulation.

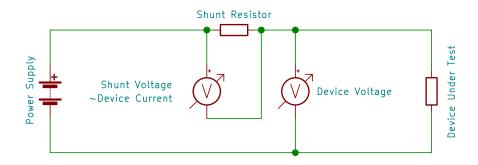

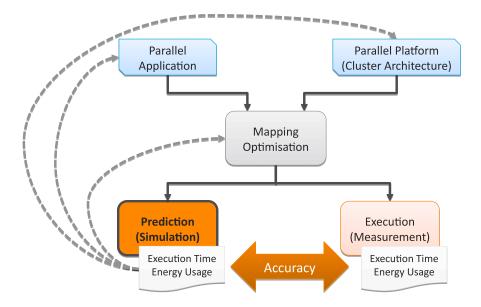

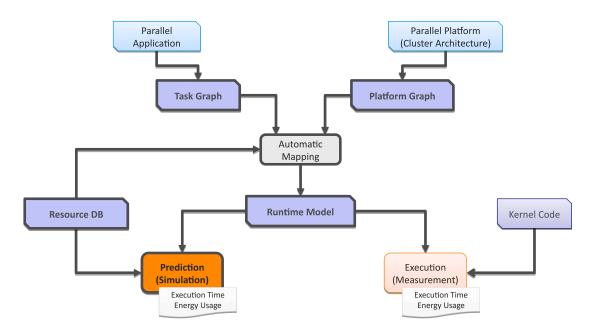

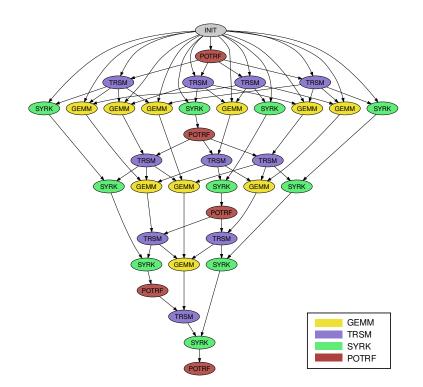

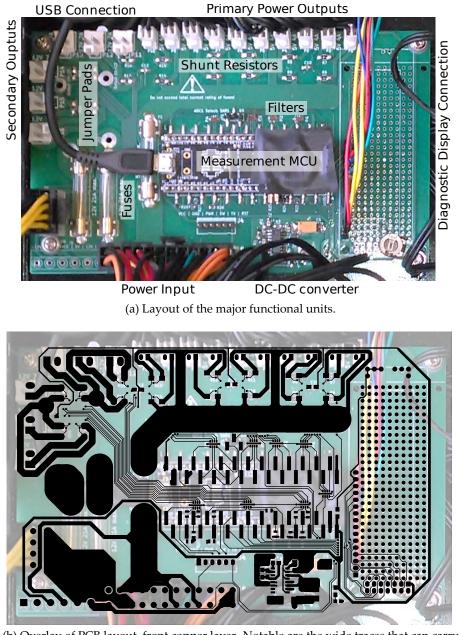

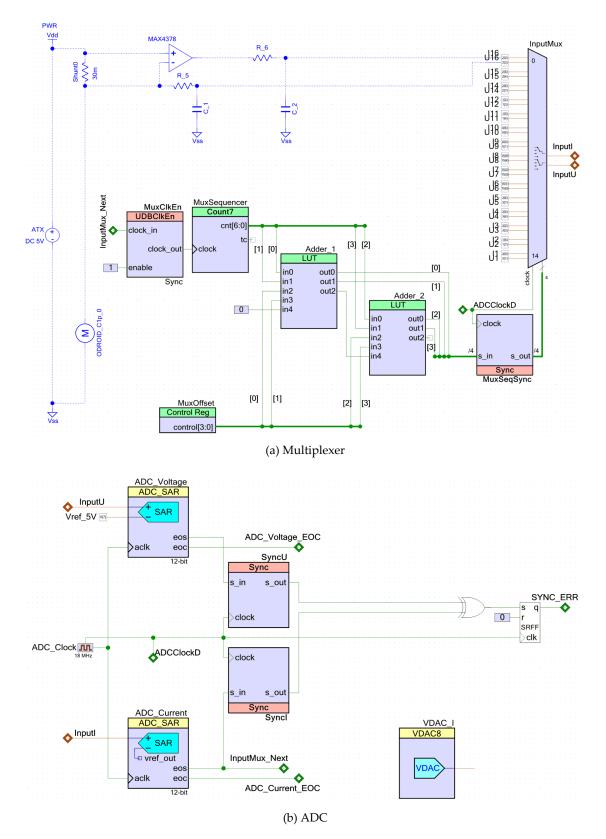

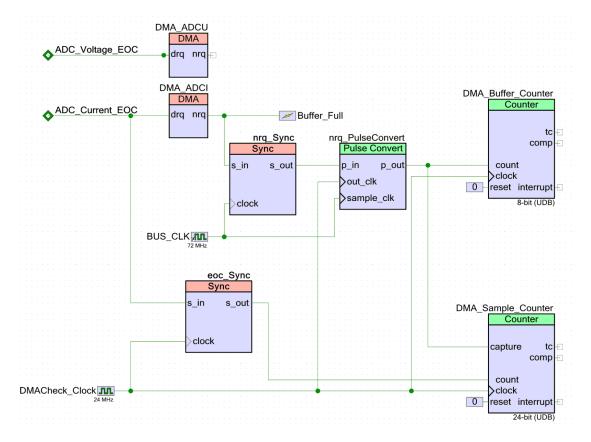

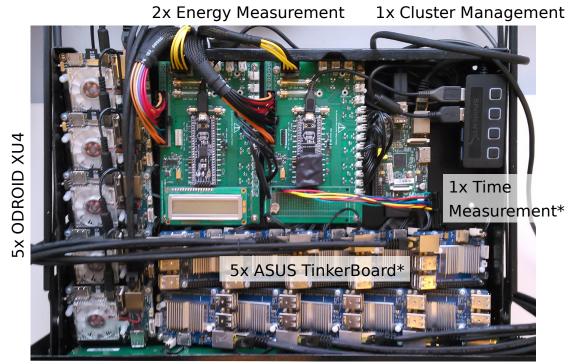

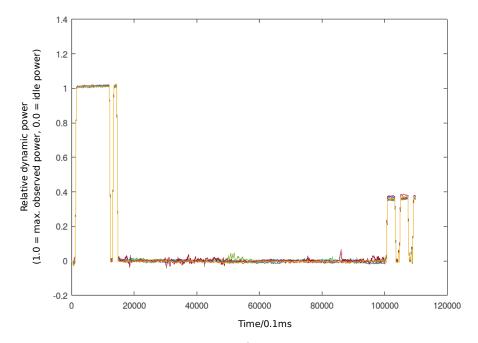

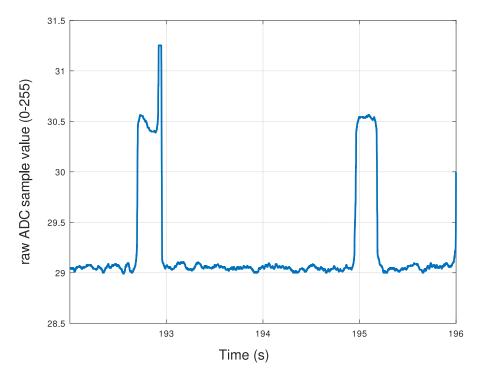

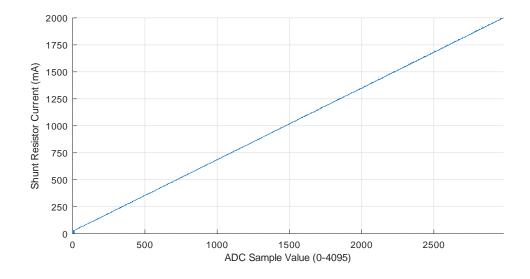

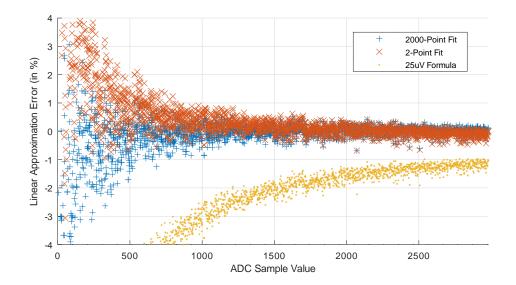

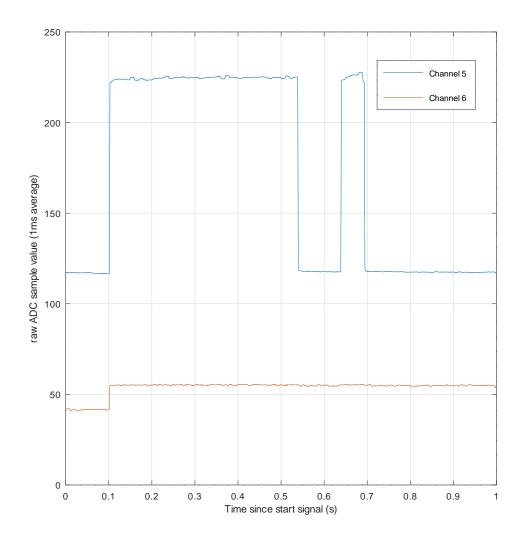

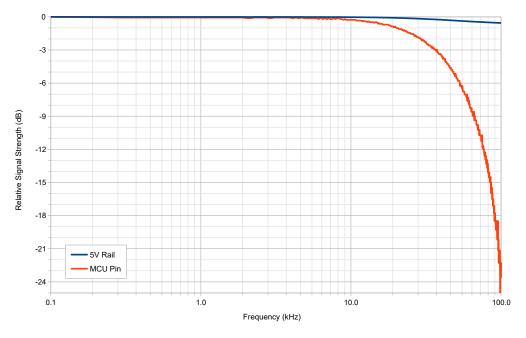

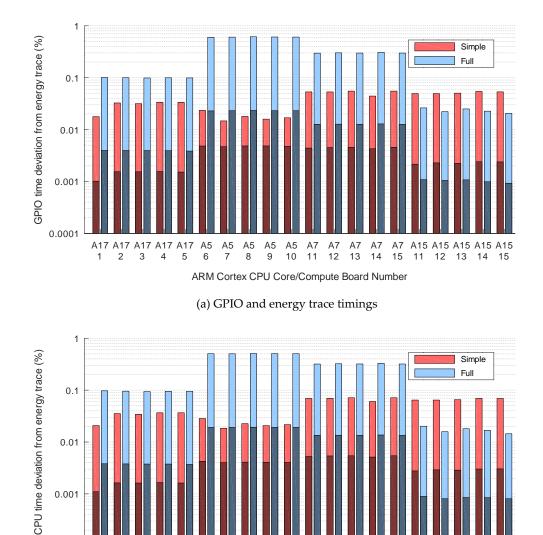

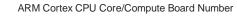

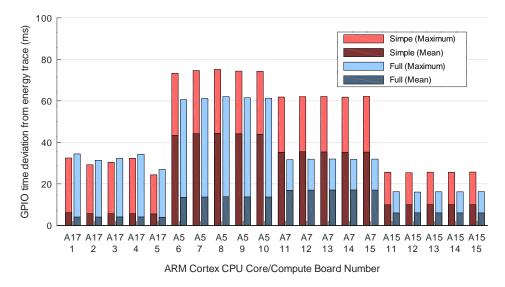

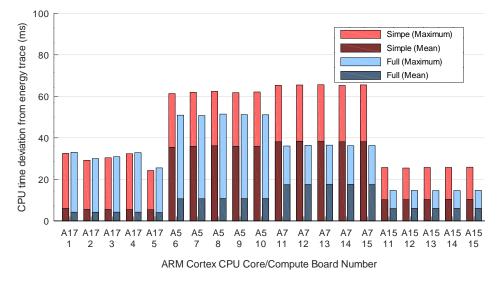

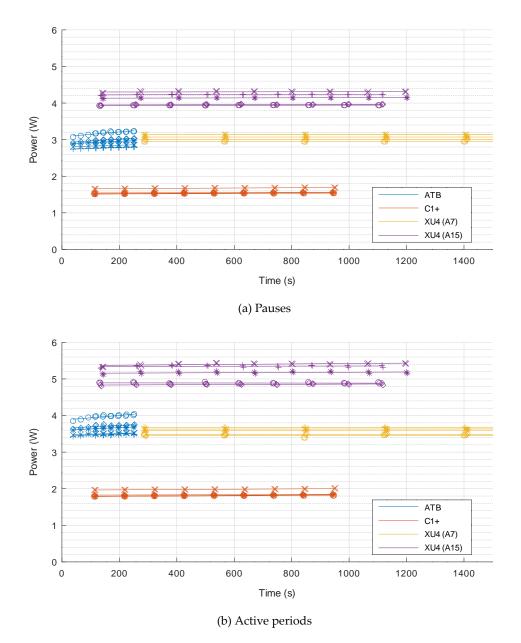

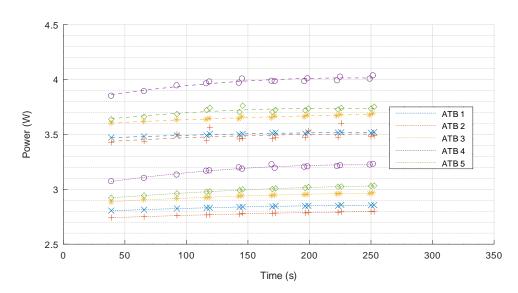

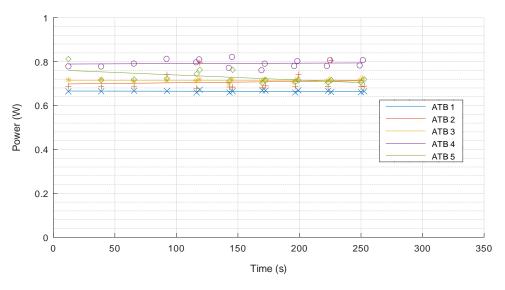

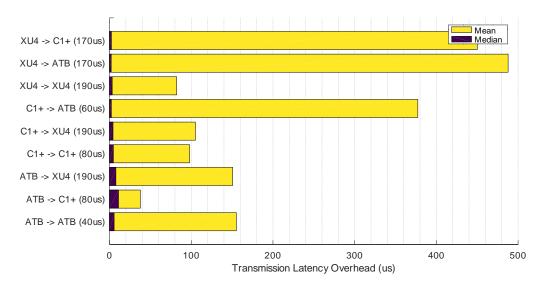

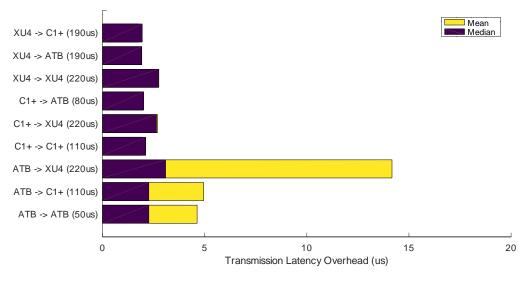

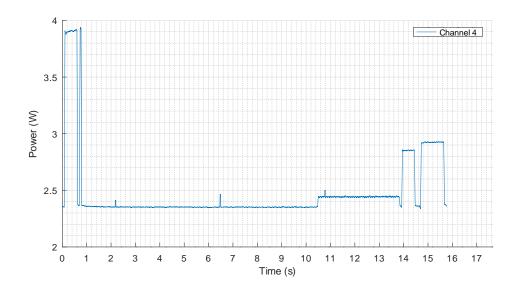

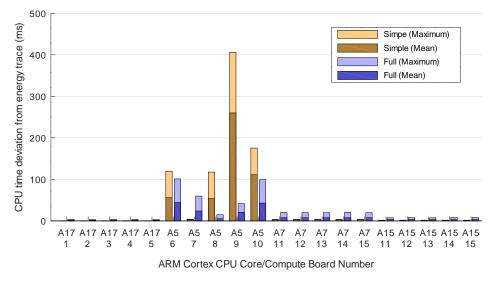

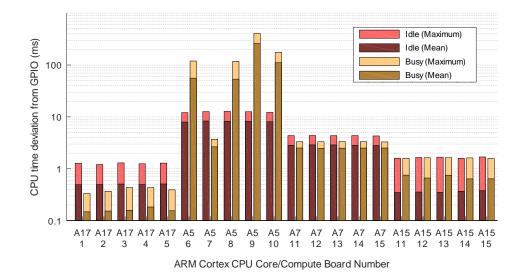

Many static scheduling algorithms use a simple weighted approach in which tasks and dependencies have abstract weights assigned to them that represent relative resource usage. Instead of providing measurements, weights can be assigned through extrapolation of previous observations (i. e. guessing), expert estimation (i. e. guessing), or just by guessing.