Fakultät II – Informatik, Wirtschafts- und Rechtswissenschaften Department für Informatik

# RT-Level Power-Gating Models optimizing Dynamic Leakage-Management

Dissertation zur Erlangung des Grades eines Doktors der Ingenieurwissenschaften

von

**MSc Sven Rosinger**

Gutachter:

Prof. Dr.-Ing. Wolfgang Nebel Prof. Dr.-Ing. Jürgen Teich

Tag der Disputation: 27.09.2012

# Abstract

Power-gating is the most promising run-time technique in order to reduce leakage currents in sub-100*nm* CMOS devices but its application is associated with numerous problems. Overhead costs in terms of additional state transition costs occur, the targeted circuit is slowed down while being in the active state, additional interfacing circuits are necessary, and in general the total impact of the power-gating technique is hard to predict at early design stages.

The goal of this thesis is to develop power-gating models for functional units at RT-level to enable design tradeoffs and to optimize the high-level synthesis for the use of this design technique.

Main contributions of this work are

- Fast and accurate power-gating models for an estimation of the functional unit's energy demand during the static active and sleep state as well as during a state transition,

- Optimized scheduling, binding, and allocation approaches that are able to increase the profitability of a cycle-wise power-gating and to expand the design-space exploration, and

- A consistent design flow of the high-level synthesis decisions to subsequent design tools.

In this thesis, such an estimation and optimization framework is proposed. The models are characterized by circuit-level simulations and have been evaluated to lead to maximum errors of 15.7% at a standard deviation of 3.41%. They are used to estimate the energy reduction of functional RT-level components to be 46% in average. The optimized synthesis approaches can even further reduce the remaining energy demand by up to 43% at an average reduction of 19.8%.

# Contents

| 1 | Intro | oductio | on la constante de la constante | 1  |

|---|-------|---------|-----------------------------------------------------------------------------------------------------------------|----|

|   | 1.1   | Low L   | eakage Design and Dynamic Power-Management                                                                      | 1  |

|   | 1.2   | System  | n Level Design and the Need for High-Level Synthesis                                                            | 2  |

|   | 1.3   | Scope   | and Contributions of this Thesis                                                                                | 3  |

|   | 1.4   | Thesis  | Outline                                                                                                         | 5  |

| 2 | Bas   | ic Con  | cepts and Background                                                                                            | 7  |

|   | 2.1   | Leakag  | ge                                                                                                              | 7  |

|   |       | 2.1.1   | Subthreshold Leakage                                                                                            | 8  |

|   |       | 2.1.2   | Gate Leakage                                                                                                    | 9  |

|   |       | 2.1.3   | Leakage-Management Methodologies Overview                                                                       | 9  |

|   |       | 2.1.4   | Summary                                                                                                         | 12 |

|   | 2.2   | Power   | -Gating in Detail                                                                                               | 12 |

|   |       | 2.2.1   | Microarchitectural Implementation of Power-Gating                                                               | 15 |

|   |       | 2.2.2   | Granularity of Application                                                                                      | 16 |

|   |       | 2.2.3   | Interfacing to Power-Gated Circuits                                                                             | 20 |

|   |       | 2.2.4   | Advanced Concepts                                                                                               | 20 |

|   |       | 2.2.5   | Summary                                                                                                         | 23 |

|   | 2.3   | High-I  | Level Synthesis                                                                                                 | 23 |

|   |       | 2.3.1   | Summary                                                                                                         | 26 |

| 3 | Rela  | ated We | ork                                                                                                             | 27 |

|   | 3.1   | Model   | ing and Estimation for Power-Gating                                                                             | 27 |

|   |       | 3.1.1   | Sleep Transistor Sizing                                                                                         | 27 |

|   |       | 3.1.2   | On-State Estimation                                                                                             | 28 |

|   |       | 3.1.3   | Off-State Estimation                                                                                            | 29 |

|   |       | 3.1.4   | Power-Up Current and Energy Estimation                                                                          | 30 |

|   |       | 3.1.5   | Additional Overhead Cost Estimation                                                                             | 31 |

|   |       | 3.1.6   | Summary                                                                                                         | 31 |

|   | 3.2   | Leakag  | ge-Management in High-Level Synthesis                                                                           | 32 |

|   | 3.3   | Industr | rial Toolflows for Power-Gating Estimation                                                                      | 34 |

|   | 3.4   | Industr | rial Power Standards                                                                                            | 35 |

|   | 3.5   | Summ    | ary                                                                                                             | 36 |

| 4 | Мос | deling a | and Estimation Flow for Power-Gating                      | 37 |

|---|-----|----------|-----------------------------------------------------------|----|

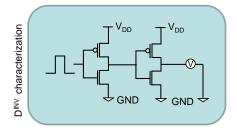

|   | 4.1 | Model    | Characterization Environment                              | 37 |

|   | 4.2 | Power-   | Gateable Functional Units                                 | 39 |

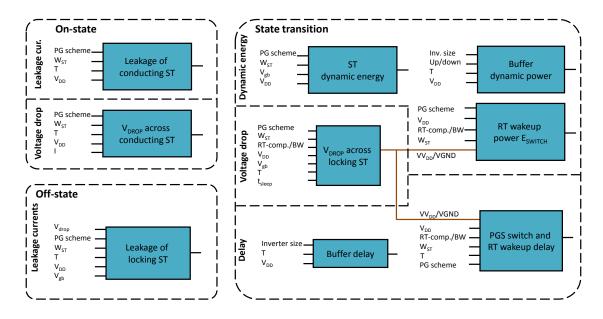

|   |     | 4.2.1    | Sub-Model Description                                     | 39 |

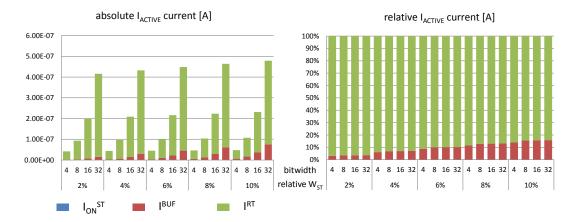

|   |     | 4.2.2    | Analysis of Power-Gating Circuitry Overhead Costs         | 41 |

|   |     | 4.2.3    | Power-Gating Scheme Leakage Models                        | 43 |

|   |     | 4.2.4    | Power-Gating Scheme Voltage Drop Models                   | 44 |

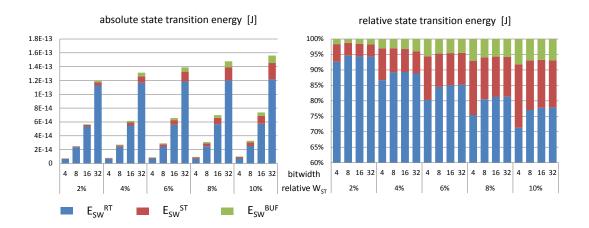

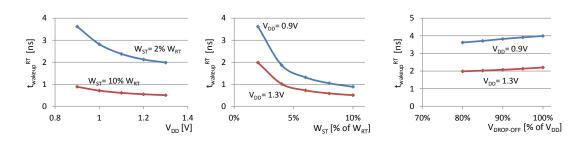

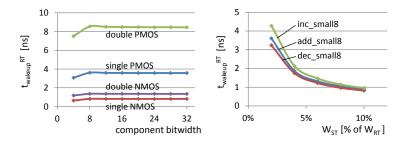

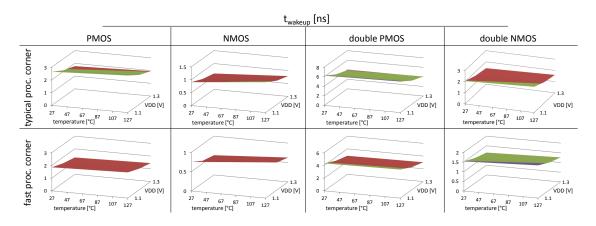

|   |     | 4.2.5    | State Transition Energy Models                            | 47 |

|   |     | 4.2.6    | State Transition Delay Models                             | 51 |

|   |     | 4.2.7    | Summary                                                   | 53 |

|   | 4.3 | Model    | Application and Estimation Flow                           | 53 |

|   |     | 4.3.1    | Prerequisites                                             | 54 |

|   |     | 4.3.2    | Simulation-based Cycle-accurate RTL Estimation            | 54 |

|   |     | 4.3.3    | System-Level Modeling                                     | 57 |

|   |     | 4.3.4    | Summary                                                   | 58 |

|   | 4.4 | Summa    | ary                                                       | 58 |

| 5 | Dyn | amic L   | eakage-Management during High-Level Synthesis             | 59 |

|   | 5.1 | Delay-   | dependent Sleep Transistor Sizing                         | 60 |

|   | 5.2 | Low L    | eakage Functional Unit Scheduling                         | 60 |

|   |     | 5.2.1    | Constraining the Control Step Assignment                  | 62 |

|   |     | 5.2.2    | Preservation of Data Dependencies                         | 62 |

|   |     | 5.2.3    | Cost Functions                                            | 63 |

|   |     | 5.2.4    | Summary                                                   | 66 |

|   | 5.3 | Low L    | eakage Functional Unit Allocation and Binding             | 66 |

|   |     | 5.3.1    | Energy Cost Representations                               | 67 |

|   |     | 5.3.2    | Resource Constrained Lower Bound Computation              | 70 |

|   |     | 5.3.3    | Relaxation of Lower Bound Binding                         | 71 |

|   |     | 5.3.4    | Allocation Optimization                                   | 71 |

|   |     | 5.3.5    | Summary                                                   | 71 |

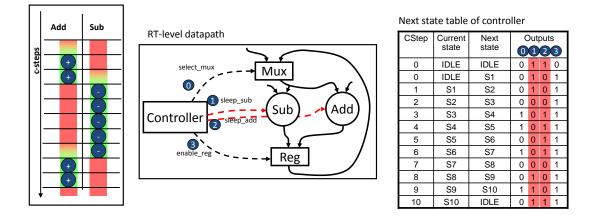

|   | 5.4 | Power-   | Management Controller Synthesis                           | 72 |

|   | 5.5 | Summa    | ary                                                       | 75 |

| 6 | Exp | erimen   | tal Environment and Assessment                            | 77 |

|   | 6.1 | Techno   | blogy Selection and Parameter Ranges                      | 77 |

|   | 6.2 | Power-   | Gating Model Evaluation                                   | 78 |

|   |     | 6.2.1    | Evaluation Results of the Sleep Transistor Leakage Models | 79 |

|   |     | 6.2.2    | Evaluation Results of the Voltage Drop Models             | 79 |

|   |     | 6.2.3    | Evaluation Results of the State Transition Energy Models  | 84 |

|   |     | 6.2.4    | Evaluation Results of the State Transition Delay Models   | 87 |

|   |     | 6.2.5    | Coupled Model Evaluation                                  | 89 |

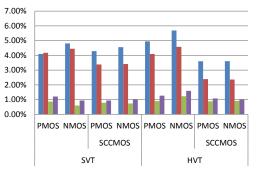

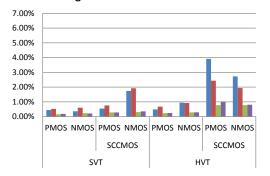

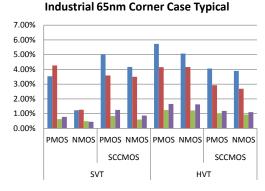

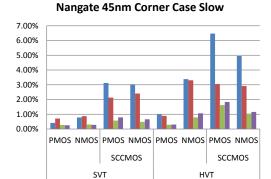

|                 |                  | 6.2.6   | Evaluation of Process Variation on Power-Gating  | 90  |  |  |  |

|-----------------|------------------|---------|--------------------------------------------------|-----|--|--|--|

|                 |                  | 6.2.7   | Summary                                          | 91  |  |  |  |

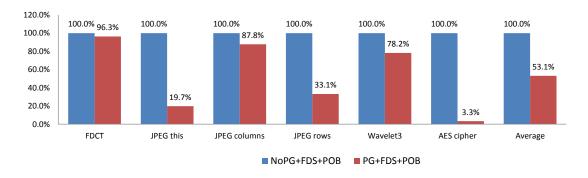

|                 | 6.3              | System  | n-level Power-Management Evaluation              | 91  |  |  |  |

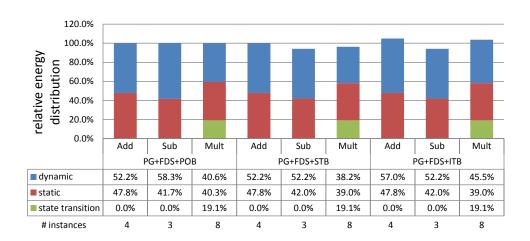

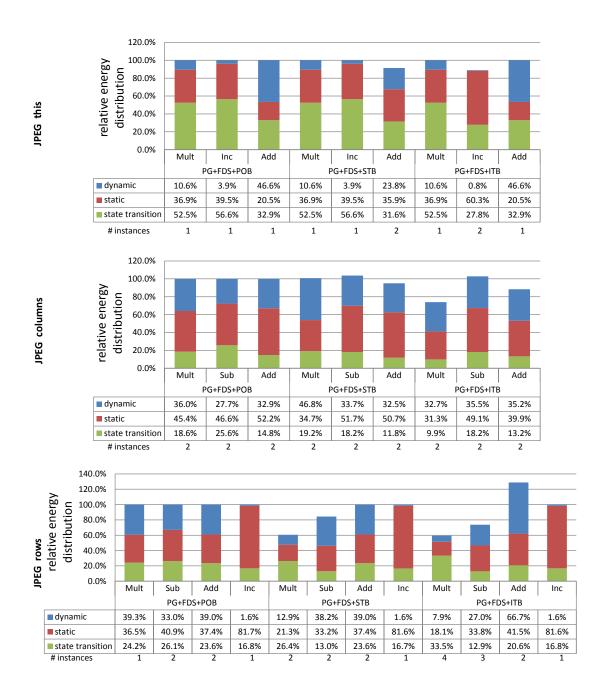

|                 | 6.4              | Power-  | Management aware High-Level Synthesis Evaluation | 95  |  |  |  |

|                 |                  | 6.4.1   | Evaluation of Cycle-Accurate RTL Estimation      | 96  |  |  |  |

|                 |                  | 6.4.2   | Binding and Allocation Evaluation                | 97  |  |  |  |

|                 |                  | 6.4.3   | Scheduler Evaluation                             | 101 |  |  |  |

|                 |                  | 6.4.4   | Summary                                          | 105 |  |  |  |

|                 | 6.5              | Compl   | iance with Industrial Power Standards            | 106 |  |  |  |

|                 | 6.6              | Discus  | sion and Summary                                 | 111 |  |  |  |

| 7               | Sun              | nmary a | and Conclusion                                   | 113 |  |  |  |

|                 | 7.1              | Outloo  | k                                                | 114 |  |  |  |

| Sy              | /mbo             | ls      |                                                  | 115 |  |  |  |

| A               | crony            | vms     |                                                  | 119 |  |  |  |

| Bi              | bliog            | raphy   |                                                  | 129 |  |  |  |

| List of Figures |                  |         |                                                  |     |  |  |  |

| Li              | List of Tables   |         |                                                  |     |  |  |  |

| Li              | List of Listings |         |                                                  |     |  |  |  |

# **1** Introduction

Embedded systems' complexity has risen dramatically due to the unbroken need for computing power. At the same time, non-ideal scaling of device parameters and supply/threshold voltages, as well as manufacturing variability have become major silicon complexity concerns for the design of an application specific integrated circuit (ASIC). The situation is predicted to get even worse as main parameters such as the ASIC's power consumption and its thermal heat will limit the previous progress of shrinking the area and increasing the number of transistor devices [ITR10]. The sector of mobile devices, predicted to have 7 trillion mobile devices connecting 7 billion people in 2017 [Dav08], is especially hard hit by this development.

To tackle this super-exponential increase of complexity, crosscutting challenges are needed to be addressed. One of these challenges is *dynamic power-management (DPM)*. DPM directly counteracts the power issue, it can be applied at different levels of abstraction during design, and even strengthens future re-use of circuit parts.

In the following, the ideas of DPM for low leakage design and the design at system-level are described and motivated in terms of its impact for this thesis. Afterwards the contribution of this thesis is worked out and summarized. The thesis outline concludes this introduction.

# 1.1 Low Leakage Design and Dynamic Power-Management

Power as a design criterion has become more and more relevant already in the nineties. At the beginning, approaches only optimized for dynamic power dissipated due to capacitive charge and short-circuit currents. In today's digital integrated circuits leakage currents are responsible for the dominating part of the total energy consumption. Especially in low utilized parts of the circuit, energy is wasted as a result of leakage currents. As a consequence, leakage has become the primary optimization goal.

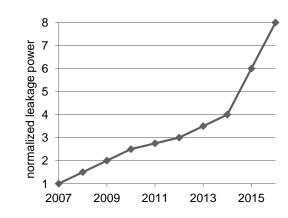

Figure 1.1 presents a full-chip leakage power foresight of the international technology roadmap for semiconductors (ITRS) working group. Their leakage prediction is based on detailed parameter estimates done in [ITR10] and is normalized to the values of 2007. In comparison with the past years, the short-term foresight predicts a slackening increase of leakage currents. This is mainly due to development of high-k dielectric materials used in semiconductor manufacturing processes limiting gate-leakage. But for the long-term, other leakage sources will gain in importance and again considerable increases in leakage currents are predicted.

In the actual ITRS 2009 Design Edition and its 2010 update [ITR10], the working group appoints leakage to a *control requirement*. Further, dynamic power-management is considered as one of the cross-cutting challenges between silicon- and system-complexity concerns. However, *DPM* is more a collective term describing techniques at various levels of abstraction. All of them have in common to aim at

Figure 1.1: Full-chip leakage foresight of ITRS [ITR10] (normalized to 2007)

dynamic-power or leakage-power savings. In contrast to improvements of the semiconductor manufacturing process and the use of new materials these DPM techniques are integrated during design, and power savings are gained during runtime by setting circuit parts into power saving states.

# 1.2 System Level Design and the Need for High-Level Synthesis

At system-level a designer has greatest possible degrees of freedom in terms of the design optimization. Functional tasks have to be partitioned to either hardware or software and adequate structural objects such as processor cores, memories, busses, and intellectual property (IP)-components have to be selected or designed for their execution. A special focus at system-level is on reuse of legacy IP-components to ease the development and to reduce costs. If not available or not compliant with constraints on quality, execution time, or power, IP-components have to be created from scratch by synthesis approaches.

Power constraints at system-level that may be derived from requirements on battery run-time rise the need for application of DPM techniques. Questions thereby are often related to the granularity of its appliance and effectiveness. Additionally, runtime-effects that are induced by the technique and the influence of parameters such as surrounding temperature are of concern. Thereby, two main problems exist for that no manufacturable solutions are available [ITR10]. The first problem is to accurately analyze and estimate power-management techniques budgeting area, power, and timing. Secondly, methods and tools for an automated insertion of power-management structures are missing. Both issues are at odds with the reuse of IP-components that are not capable to power-manage and demand for PM-integrated IP-components. A supplementary insertion of internal PM-techniques is not possible in many cases and even an externally caused power-down may not be acceptable due to a state-loss of the component.

As a result, appropriate high-level synthesis (HLS) methods and tools to design DPM-aware IP components are needed. These tools have to comprise DPM-techniques directly during synthesis and have to offer PM-interfaces at system-level.

Table 1.1 shows a market survey on the most common available behavioral level synthesis tools. The

| Vendor   | Tool                    | I/O languages           |  |  |

|----------|-------------------------|-------------------------|--|--|

| Synopsys | SynphonyC Compiler      | C, C++ / Verilog, VHDL  |  |  |

| Forte    | Cynthesizer             | SystemC-TLM / Verilog   |  |  |

| NEC      | Behavioral Synthesizer  | C / VHDL, Verilog       |  |  |

| Bluespec | Bluespec Compiler       | Sys. Verilog, SystemC / |  |  |

|          |                         | Verilog, SystemC        |  |  |

| AutoESL  | AutoPilot               | C, C++, SystemC /       |  |  |

|          |                         | Verilog, VHDL, SystemC  |  |  |

| Mentor   | Catapult C Synthesis    | C, C++ / Verilog, VHDL  |  |  |

| CebaTech | C-to-RTL-Compiler (C2R) | C / Verilog             |  |  |

Table 1.1: Market survey on behavioral synthesis tools

minority of the tools address leakage estimation. Further, none of the tools currently targets leakage optimization and is capable to implement dynamic power-management during synthesis. Thus all tools are candidates for the integration of the flow presented in this thesis.

## 1.3 Scope and Contributions of this Thesis

In this thesis the following terminology will be used, defining the terms device, component, system, and circuit.

- A single transistor is referred to as device. A single sleep transistor is denoted as device.

- **Components** refer to register transfer level (RTL) components. Examples to be mentioned here are adders, multipliers, registers, and multiplexers.

- More complex datapaths containing multiple RTL components including a dedicated controller are referred to as system.

- The term **circuit** is used in a lax manner and is not necessarily fixed to a level of abstraction. For example, several design techniques can be applied to single gates, components, or even systems. To signify this flexibility the term circuit is used.

Several research projects at the institute for information technology OFFIS aimed at the estimation and optimization of power in ASIC designs. At the beginning the focus was on dynamic power. Later, leakage power estimation and its *static optimization* gained importance. At the same time the level of abstraction raised from transistor- to behavioral-level.

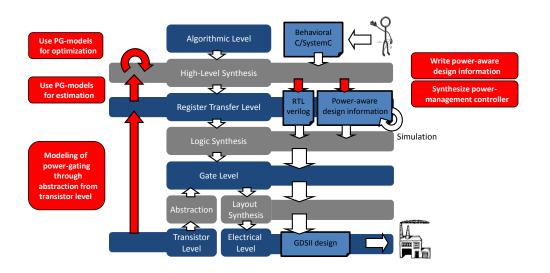

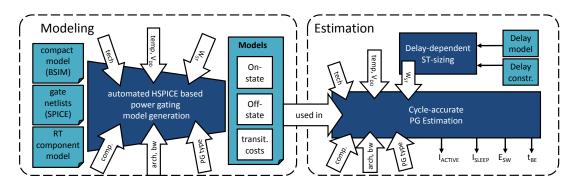

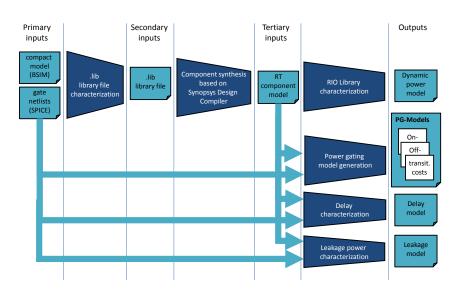

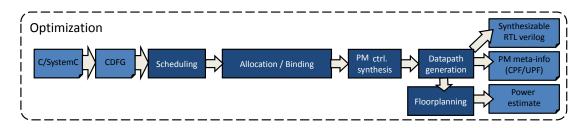

The idea of this thesis is to logically continue previous work by including *DPM* techniques to target leakage optimization during runtime of a design. Thereby, the scope is on power-gating that is applied to functional RT-level units of ASIC designs as adders or multipliers. Figure 1.2 gives an overview on the four-folded flow that is proposed. It is divided into a *modeling-*, *estimation-*, *optimization-*, and *output generation-*part leading to a holistic IP-synthesis flow with the consideration of dynamic leakage-management.

#### 1 Introduction

Figure 1.2: Visualization of proposed power-gating modeling, estimation, and optimization flow

The main contributions of the thesis are summarized in the following:

#### • A discussion of power-gating estimation and its granularity problem.

Power-gating estimation implicates a huge bunch of parameters that impact resulting leakage savings. In contrast to simple cell-based gating approaches, in this thesis power-gating is applied to RTL components that even complicates its estimation. Transistor-level simulations are applied to identify important parameters and also to explore temporal restrictions on the application of powergating.

#### • The definition of requirements on power-gating RT-level models.

The superordinated goals of the models are to enable automated decisions on temporal granularity of power-gating application based on break-even times and high-level design tradeoffs. Therefore, it is necessary to predict leakage currents in active and standby state, wake-up time and costs, virtual supply or ground voltages in standby state, and area overhead under consideration of all important parameters.

## • A widely automated model characterization process.

A power-gating modeling process through abstraction from transistor level is implemented to perform an automated characterization for a given transistor technology and its parameters (see Figure 1.2). The set of derived models allows a holistic, cycle-accurate, and fast estimation of power gated RT-components. Combined with only few characterization data, this modeling approach builds a cornerstone of the following high-level leakage optimization.

## • An estimation flow for RT-level power-gating.

The power-gating models are completely integrated into the cycle-accurate power estimation of the PowerOpt<sup>®</sup> high-level synthesis tool that implements the algorithmic- to RT-level synthesis.

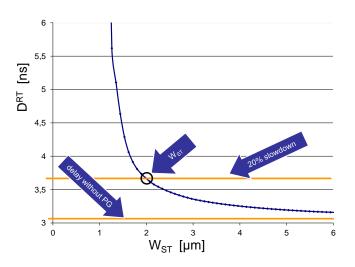

Thereby, the dimensioning of sleep transistors implies a tradeoff between faster computation and less leakage. To relieve the designer from decisions on transistor level, a delay-dependent sleep-transistor sizing approach enables a completely automated estimation.

### • A dynamic leakage-management methodology applied during high-level synthesis.

Two approaches are implemented to enhance the high-level synthesis in terms of the application of dynamic leakage-management techniques. Firstly, an operator binding and allocation approach that minimizes both, static and dynamic power is proposed. In contrast to existing works it incorporates different power modes into synthesis and optimizes for an efficient use of power-management. Secondly, the optimization criterion of the scheduling is changed into a heuristic for improving the effectiveness of techniques such as power-gating. The proposed ILP-formulated scheduling performs an operation clustering within the execution-time of the critical path and serves as a heuristic to minimize the amount of power state transitions. The resulting schedule further improves the binding and allocation phase and operations can be bound to resources cluster-wise. As a result, emerging idle times can be exploited by power-management techniques. Both, the low leakage allocation and the scheduling are integrated into OFFIS's PowerOpt<sup>®</sup> tool.

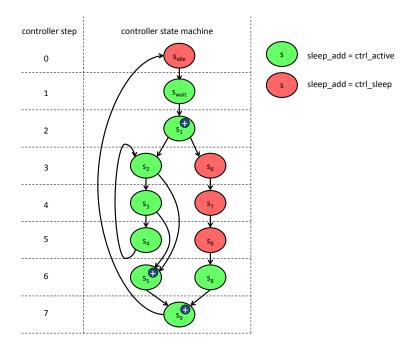

#### • A power manager controller synthesis.

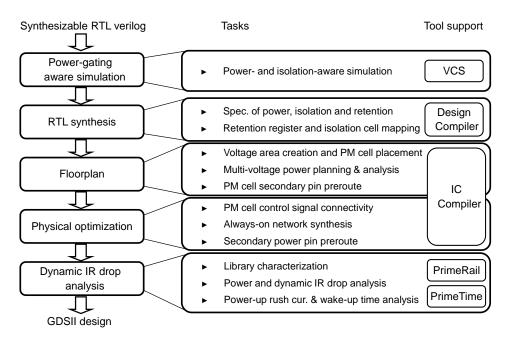

Power-management at architectural level raises the problem of its controllability during runtime. The datapath is expanded by control signals from the controller to the components. During synthesis, the controller is extended to a power manager by a static analysis of the fixed schedule. It is further shown that the adoption of the datapath is compliant to industrial standards and that the results of the *output processing* can be passed to subsequent tools (see Figure 1.2).

#### • The evaluation of the model characterization.

The models are evaluated with different transistor technologies, types of power-gating, components, and parameters. Parameters are varied within their possible ranges, and error measures are applied. The models are further used to analyze possible savings at system-level.

#### • The evaluation of the leakage-management methodology.

In the second part of the evaluation the models are applied within the new behavioral synthesis flow. The analysis bases on several practical examples. The results are compared to results of previous high-level synthesis algorithms known in literature and improvements of the power consumption are discussed.

# 1.4 Thesis Outline

The rest of this thesis is organized as follows: The next chapter briefly describes basic concepts and background information on leakage currents and its management technique applied in this thesis. Additionally, fundamental tasks of the high-level synthesis are presented. Chapter 3 contains a short presentation of existing power standards to unify the application of power-management across different levels of abstraction. It also includes a presentation of the state-of-the-art in modeling, estimation, and optimization from both, industry and research. The modeling and estimation flow is described in Chapter 4 including its simulation environment. The models are then applied within a leakage-minimizing high-level synthesis. Chapter 5 proposes the new leakage-optimized allocation, binding, and scheduling. Additionally, necessary enhancements of the controller synthesis are described to take an advantage of the power-manageable datapath. In Chapter 6 the models are evaluated based on a selection of technologies and the improvements of the power-management (PM)-aware synthesis are analyzed on different practical design examples. The thesis closes with a short summary, conclusion, and outlook in Chapter 7.

# 2 Basic Concepts and Background

In the following basic concepts, techniques, and background information are presented. Section 2.1 describes leakage currents with its sources and factors and gives an overview on techniques for its reduction. The most promising technique, power-gating, is described in detail in Section 2.2. Fundamentals of the high level synthesis, as it is being optimized in this thesis, are presented in Section 2.3. The following presentation explicitly is not an exhaustive description on these topics but summarizes aspects that are necessary as prerequisites for the subsequent chapters.

## 2.1 Leakage

The two states of a transistor are getting closer since the supply voltage swing as well as the threshold voltage are getting smaller and smaller. Additionally, transistor scaling reaches atomic scale and forces quantal effects. In a consequence, the picture of a transistor being a perfect digital switch with two clearly defined states developed more and more into the direction of becoming an analog and leaky switch.

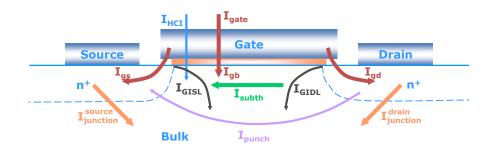

Figure 2.1 [Hel09] shows a cross-section through an n-channel metal-oxide semiconductor (NMOS) transistor with different kinds of present leakage currents. While locking, drain is typically at a high potential and all other terminals are at low. In this state a subthreshold current  $I_{subth}$  flows through the channel, a gate tunneling induced current  $I_{gate}$  occurs from gate to source/drain/bulk, a punchthrough current  $I_{punch}$  flows from drain to source when both pn-junctions touch each other, an unavoidable current  $I_{junction}$  flows though the pn junctions, and a current is induced from gate to source  $I_{gisl}$  and drain  $I_{gidl}$  in the gate-(drain/source) overlapping area. If the channel is conducting, source, drain, and gate have the same potential and thus only gate- and pn-junction leakage occur. During switching hot carrier injection occurs where electrons or positive charge carriers overcome the potential barrier and are injected into the gate dielectric leading to a current  $I_{hci}$  from gate to the channel.

From a historical point of view, these currents represented a vanishing part in the above-100nm age but have developed to the significant contributor of the total power dissipation as analyzed and predicted in [KAB<sup>+</sup>03], [MR03], and [ITR10]. Especially in many mobile applications large fractions of an ASIC idle most of the time and the leakage power is the only contribution during these idle times.

In the following a closer insight will be given for the two most important leakage types, subthreshold and gate leakage, in order to identify and highlight parameters of big impact. These parameters will serve as basis for the modeling process in Chapter 4. A far closer description including an exhaustive presentation of leakage currents and its parameter dependencies is given in [Hel09] and [RMMM03].

Figure 2.1: Cross-section through an NMOS transistor and different kinds of leakage currents in locking, conducting, and transient state [Hel09]

## 2.1.1 Subthreshold Leakage

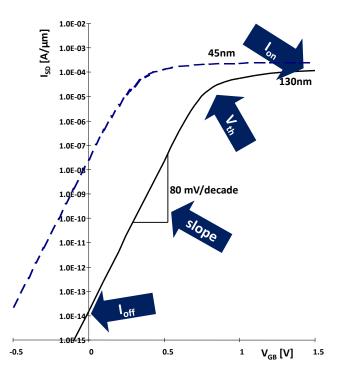

Figure 2.2 ([Hel09]) shows an  $I_{SD}/V_{GB}$ -curve of an NMOS transistors manufactured in the 45nm and 130nm predictive technology model process of [IaASU]. This curve characterizes the conductivity of a transistor as a high  $I_{ON}$  current can flow through the channel in conducting state and a lower  $I_{OFF}$  current remains while locking. The kink in the curve defines the threshold voltage  $V_{TH}$  and the characteristic slope is given for the linear part. As it can be seen,  $I_{ON}$  is in the same order of magnitude for both transistors but the remaining subthreshold leakage ( $I_{OFF}$ ) is  $10^6$  times higher for the 45nm technology.

Figure 2.2: I<sub>SD</sub>/V<sub>GB</sub>-curve of an NMOS transistor based on 45/130nm PTM process [Hel09]

The equation, describing subtreshold currents in a transistor, as it is defined in the Berkeley shortchannel IGFET model (BSIM) manual [DYX<sup>+</sup>07] and an approximation for the locking state with a drain-source voltage close to  $V_{DD}$  is given in Equation 2.1. It can be seen that subtreshold leakage scales linearly with the design parameters channel width W and length L, exponentially (dominating the quadratic impact) with the inverse thermal voltage  $V_T$  (being itself linearly dependent on the temperature T), and again exponentially with the threshold voltage  $V_{TH}$  and gate-source voltage  $V_{GS}$ .

$$I_{subth} = kV_T^2 \frac{W}{L} e^{\frac{V_{GS} - V_{TH}}{nV_T}} \left(1 - e^{-\frac{V_{DS}}{V_T}}\right) \approx \alpha e^{-\beta \frac{V_{TH}}{T}}$$

(2.1)

## 2.1.2 Gate Leakage

Today's gate isolation layers have a height of few SiO molecules. Electrons can tunnel through the isolation layer, although the potential barrier energy is higher than an electron's energy. The tunneling probability rises exponentially while the isolation layer becomes thinner and resulting unwanted currents significantly contribute to the total power dissipation. These currents flow from gate to either source ( $I_{GS}$ ) or drain ( $I_{GD}$ ) (directly in the overlapping area or through the channel), or to bulk ( $I_{GB}$ ) and occur in every transistor state. They are summarized as gate leakage.

$$I_{gate} \propto \frac{\lambda_S W V_{GS}^2 + L W V_T V_{GB} + \lambda_d W V_{GD}^2}{T_{\alpha x}^2 e^{\beta T_{\alpha x}(\alpha_0 + \alpha_1 V_{\alpha x} + \alpha_2 V_{\alpha x}^2)}}$$

(2.2)

An approximation of gate leakage currents is given in Equation 2.2. Beside the isolation layer thickness  $T_{ox}$ , gate leakage majorly depends on the gate-(source/drain) voltage  $V_{GS}/V_{GD}$  and the gate-drain/gate-source overlapping area size  $W\lambda_d$  and  $W\lambda_s$ , respectively. A temperature dependency only exists for gate-to-bulk currents but compared to  $I_{GS}$  and  $I_{GD}$ ,  $I_{GB}$  is negligible small.

## 2.1.3 Leakage-Management Methodologies Overview

Two different classes of leakage-management techniques can be separated: *static* and *dynamic* techniques. They are all considered and applied during the design but the temporal manner when leakage currents are reduced differs. Static techniques do not imply different power modes and as a consequence, beside leakage currents, they also reduce other parameters like the maximum frequency at all time. In contrast to this, dynamic techniques implicate different modes during runtime and offer more flexibility. Saving-modes might affect leakage currents, the dynamic power consumption as well as the circuits speed but if necessary, the design can operate at a normal mode. In contrast to static techniques, mode transitions become necessary and complicate the overall adoption of these techniques.

### Static Leakage-Management Techniques

**Voltage Island** Timing constraints may differ between several circuit parts of a design. This observation or given demand in combination with the superlinear dependency between leakage currents and the assigned supply voltage can lead to a subdivided design. An assignment of different supply voltages to these islands is static and needs to be known during the design phase. **Static Body Biasing** Beside the three functional terminals *drain*, *gate*, and *source* of a transistor the *body* terminal, typically connected to *source*, can be separated and loaded to an independent and different potential. This will significantly impact the channel conductivity and switching performance. It can either lead to an improved performance in the active mode if a forward-biasing is applied or to a reduced leakage current in an idle phase if a reverse-biasing is applied to the body. The latter reverse body biasing technique increases the threshold voltage  $V_{TH}$  that in turn reduces the performance and especially sub-threshold leakage currents. The static body biasing assigns fixed voltages during design in order to create low leakage or high performance circuits.

### **Dynamic Leakage-Management Techniques**

**Dynamic Body Biasing** Body voltage assignment can also be done dynamically. In this case two operating modes exist. The body voltage is forward-biased in the active mode and/or reverse-biased in the idle mode to meet the varying performance demands. For this technique, multiple voltages need to be provided and additional switches are necessary.

**Power-Gating** Power-gating (PG) is the most intuitive technique for reducing leakage currents. It introduces a power switch to temporarily power down unused parts of an ASIC design. In this state the difference in leakage currents  $I_{ACTIVE} - I_{SLEEP}$  is saved. The switch is typically made of a single transistor and is also referred to as *sleep transistor*. As simple as the idea of power-gating sounds, it is complicated to implement and to consider its impact during the design because of an immense range of implementation artifacts. Most important design parameters are the type and size of a sleep transistor, the interfacing to neighboring components, as well as the component size to which power-gating is applied. A major drawback of power-gating is the loss of the internal state during sleep.

**Minimum Leakage Vector** Exploiting the input data dependency of leakage currents is the idea of the minimal leakage vector (MLV) technique. It assigns fixed and pre-defined data vectors to the input of the target component in order to reduce its internal leakage current. Main problems of this technique are the determination of the MLV for designs with a large input bitwidth, the diminishing effect of leakage controllability by just assigning the inputs, and the state retention. Like in the PG approach the internal state will be lost.

**Dynamic Voltage and Frequency Scaling** Similar to the static voltage island assignment, the dynamic voltage and frequency scaling (DVFS) technique exploits the dependency between leakage currents and the assigned supply voltage. The difference is that both the supply voltage and frequency of a component are reduced in times of a low utilization and are not statically assigned. Main problems of implementation arise from providing multiple supply voltages and clock frequencies to the chip areas where DVFS is applied to. In contrast to PG and MLV, the state will be preserved in the DVFS approach. It can be distinguished between approaches where the component is still functional at a lower voltage and frequency and a forced application where only the state is preserved but the component is no longer able to operate.

All mentioned techniques do not come free of costs. Large computational effort for finding the MLV or complicated design decisions for finding suitable voltages and frequencies meeting all requirements are only few examples. They also have in common that the ASIC's area increases due to the need for hardware to apply the MLV, the power-gating switch, and additional routing effort for multiple bias or supply voltages.

|                                                                                                                                                                                           |       | Leakage currents [A]                                       |                                                                               |                                                            |                                                            |                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|------------------------|

| Circuit                                                                                                                                                                                   | Input | No PM                                                      | Minimum<br>leakage vector<br>assignment<br>(MLV)                              | Reverse body<br>biasing (RBB)                              | Dynamic voltage<br>and frequency<br>scaling (DVFS)         | Power-gating<br>(PG)   |

| T The                                                                                                                                                                                     | 00    | 22.0*10 <sup>-12</sup>                                     | 22.0*10 <sup>-12</sup>                                                        | 21.3*10 <sup>-12</sup>                                     | 6.7*10 <sup>-12</sup>                                      | 4.2*10 <sup>-12</sup>  |

|                                                                                                                                                                                           | 01    | 35.2*10 <sup>-12</sup>                                     |                                                                               | 22.2*10 <sup>-12</sup>                                     | 19.1*10 <sup>-12</sup>                                     |                        |

|                                                                                                                                                                                           | 10    | 38.5*10 <sup>-12</sup>                                     |                                                                               | 25.0*10 <sup>-12</sup>                                     | 20.9*10 <sup>-12</sup>                                     |                        |

| <u> </u>                                                                                                                                                                                  | 11    | 31.3*10 <sup>-12</sup>                                     |                                                                               | 11.9*10 <sup>-12</sup>                                     | 19.4*10 <sup>-12</sup>                                     |                        |

|                                                                                                                                                                                           | 0     | 308*10 <sup>-12</sup>                                      | 125*10 <sup>-12</sup>                                                         | 205*10 <sup>-12</sup>                                      | 166*10 <sup>-12</sup>                                      | 5.6*10 <sup>-12</sup>  |

|                                                                                                                                                                                           | 1     | 125*10 <sup>-12</sup>                                      |                                                                               | 48*10 <sup>-12</sup>                                       | 78*10 <sup>-12</sup>                                       | 5.0 10 **              |

| $\begin{array}{c c} \textbf{4Bit Adder} \\ a_3b_3 & a_2b_2 & a_1b_1 & a_3b_3c_4 \\ a_4b_1 & a_4b_1 & a_4b_1 \\ \hline add & fradd & fradd \\ c_{out} & s_3 & s_2 & s_1 & s_0 \end{array}$ |       | Min.: 1.82*10 <sup>.9</sup><br>Max.: 2.27*10 <sup>.9</sup> | 1.82*10 <sup>-9</sup>                                                         | Min.: 1.26*10 <sup>.9</sup><br>Max.: 1.58*10 <sup>.9</sup> | Min.: 0.81*10 <sup>.9</sup><br>Max.: 1.05*10 <sup>.9</sup> | 0.082*10 <sup>.9</sup> |

| [Industrial 45nm LP technology @ HSPICE, 1.0V, 27°C ]                                                                                                                                     |       |                                                            | V <sub>BB</sub> <sup>P</sup> = 1.2 V<br>V <sub>BB</sub> <sup>N</sup> = -0.2 V | V <sub>DD</sub> =0.6V                                      | HVT<br>NMOS cutoff                                         |                        |

Figure 2.3: Overview on possible leakage reductions induced by different leakage-management techniques

Figure 2.3 compares the different dynamic leakage-management techniques in terms of their potential leakage savings at different levels of granularity. They are all applied at a medium sized NAND-gate (smallest), a largest available inverter-gate (middle sized), and a 4bit adder component (largest circuit observed in this overview). All measurements were obtained by circuit-level simulations and refer to an industrial 45nm low power (LP) device technique at a supply voltage of 1V and an operating temperature of  $27^{\circ}$ C. At gate-level, leakage measurements are listed for all possible input-vectors, whereas at RT-level minimum and maximum currents are presented.

It can be seen that the leakage reduction due to MLV-assignment diminishes from 40 - 60% at gateto 20% at RT-level and will lead to the smallest possible savings. Reverse body biasing (RBB) and DVFS will result in savings of 30 - 70% with an offset voltage of 0.2V for RBB and a reduced supply voltage of 0.6V for DVFS. Power-gating outperforms these improvements by far and will result in savings up to 95%. Each circuit is power-gated by one smallest available NMOS sleep transistor in the high threshold voltage (HVT) version. It can impressively be seen that the fine-grained appliance of power-gating limits the savings of the NAND-gate to about 87%. This is because the channel-width ratio between the sleep transistor and the transistors in the power-gated circuit is much bigger for a small circuit and thus powergating is less effective. In turn, power-gating is more effective the larger the power-gated circuit is.

## 2.1.4 Summary

Leakage currents constitute in the same order of magnitude to the total power consumption of today's semiconductor designs as the dynamic power due to capacitance charging. In circuits with a bigger part of idleness the fraction of leakage currents is even higher and dominates the total power dissipation. The encouraging factors of leakage can be separated into dynamic and static parameters. Dynamic parameters may change during runtime and can be set from outside such as the surrounding temperature, supply or body voltage. Static parameters are fixed during manufacturing such as the gate oxide thickness, type and level of doping concentration, and are encapsulated in the semiconductor technology.

Beside manufacturing techniques such as high-k dielectrics (to counteract gate leakage currents) or future FinFET design (three-dimensional channels for a better channel blocking to reduce subthreshold currents), dynamic power-management gained the most important class of runtime techniques. As analyzed on example circuits, power-gating has the biggest impact on all kinds of leakage currents and may cut off more than 90% of them.

## 2.2 Power-Gating in Detail

Transistor stacking is one of the most important inventions for the design of digital integrated circuits. It has been introduced in 1963 in the complementary metal-oxide semiconductor (CMOS) technique where stacked and complementary switching pull-up and pull-down networks prevent a circuit from high short-circuit currents to flow from supply to ground through the transistor channels.

This principal of transistor stacking is also used for power-gating that has been invented by M. Horiguchi, T. Sakata and K. Itoh in 1993 [HSI93]. Beside the pull-up and pull-down network a third network is connected in series, either above the pull-up or below the pull-down network. It contains a functionally-redundant switch in terms of a p-type transistor header or n-type transistor footer device. While this transistor is closed, it is intended to be as transparently as possible regarding the functionality of the circuit. In the open state it controls the supply or ground voltage and thus power-gates a circuit. Its purpose is again to reduce currents but, in contrast to the CMOS methodology the focus is on leakage currents occurring as described in Section 2.1. During this state, the circuit is *sleeping* and not able to operate. Thus, power-gating can only be applied during times of disuse.

In the following, the impact of this additional transistor will be discussed in detail for the two static states as well as for the state transition. All observable and important currents, voltages, and other parameters are defined. Section 2.2.1 then shows different possible implementation schemes described in literature. The block size, to which power-gating is applied, is discussed in Section 2.2.2 followed by interfacing considerations in Section 2.2.3. Finally, Section 2.2.4 proposes more advanced and probably future concepts of power-gated designs.

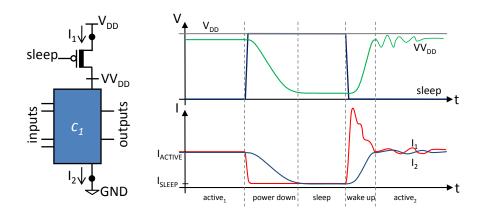

#### Trace of a Power-Down Sequence

Figure 2.4 schematically illustrates a sequence of powering down and waking up a circuit block  $c_1$  with a p-type header device. The circuit is controlled by a *sleep* signal and two characteristic currents  $I_1$  and  $I_2$  are plotted over time. The sequence is divided into the following phases. *active*<sub>1</sub> describes a phase of

idleness. At this time  $c_1$  has constant in- and outputs and the overall system is stable. In the second phase *power down*, the switch is opened and the circuit  $c_1$  powers down until it enters the following static *sleep* phase. After a while,  $c_1$  is woken up (*wake up*) and traverses a second active phase *active*<sub>2</sub>.

Figure 2.4: p-type power-gating functionality

**Static active state** In the active modes, the sleep transistor conducts but it cannot be prevented that a small IR drop  $V_{DROP-ON}^{ST}$  occurs across the sleep transistor. This is because the transistor retains a small resistance  $R_{ST}(t)$  while conducting. The series connection of sleep transistor and circuit acts as a voltage divider with a comparatively small sleep transistor resistance and high circuit resistance. Both resistances vary over time dependent on the data input signals of  $c_1$  as they cause internal activations. As a consequence, the effective circuit's supply voltage reduces to a so-called virtual supply voltage  $VV_{DD}$ . If an NMOS-device is used for power-gating, the ground voltage is raised to a virtual ground level VGND. The voltage drop  $V_{DROP-ON}^{ST}$  across the sleep transistor is thus defined as:

$$V_{DROP-ON}^{ST}(t) = \begin{cases} V_{DD} - VV_{DD}(t) & \text{for p-type power-gating} \\ VGND(t) & \text{for n-type power-gating} \end{cases}$$

(2.3)

In both cases, the effective supply voltage of  $c_1$  is defined as:

$$V_{DD}^{eff}(t) = V_{DD} - V_{DROP-ON}^{ST}(t)$$

$$(2.4)$$

As an important consequence, the delay of a circuit increases because it is a function of the effective supply voltage.

Figure 2.4 distinguishes between two active scenarios. In  $active_1$ , the data inputs of the circuit are fixed and the overall system is in a stable idle state. As it can be seen, the virtual supply voltage  $VV_{DD}$  as well as the leakage current  $I_{ACTIVE}$  are constant. In  $active_2$ , the input signals of  $c_1$  change their values. During this phase, switching activity propagates within  $c_1$  until the stable state of  $active_1$  is reached. It can be seen that an activity induced current flow impacts the division of  $VV_{DD}$  and  $V_{DROP-ON}^{ST}$ .

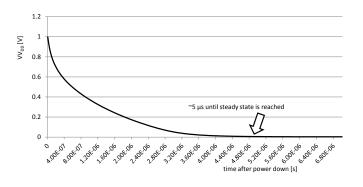

**Transient power-down state** From the moment of activating the power switch,  $VV_{DD}$  drops with time until it saturates at a voltage close to GND. At the same time  $I_1$  and  $I_2$  reduce to  $I_{OFF}$  that is limited to the subthreshold and gate leakage current through the sleep transistor. As shown,  $I_1$  and  $I_2$  diminish with a different rate. While  $I_1$  is cut by a sharp edge as *sleep* passes  $V_{TH}$ ,  $I_2$  decreases slowly and discharges the capacitances in  $c_1$ . During this phase, the state within memory elements of  $c_1$  is lost if no further state-preserving techniques are applied as presented in Section 2.2.4. The time for powering down to the static sleep state is denoted as  $t_{powerdown}$ .

**Static sleep state** In the *sleep* state,  $I_1$  only describes remaining leakage currents that are effectively reduced. In this stable state,  $I_1$  defines  $I_{SLEEP}$  and depends on the saturated voltage level at  $VV_{DD}$  that in turns depends on the resistance ratio between sleep transistor and power-gated circuit. In the end,  $I_{SLEEP}$  is a function of several parameters such as transistor technology, power-gated circuit  $c_1$ ,  $c_1$ 's inputs, sleep transistor parameters (i.e.  $W_{ST}$ ,  $V_{TH}$ , ...), or ambient temperature.

$I_2$  levels out at a slightly higher current compared to  $I_1$  because gate-leakage currents from logically high inputs flow through the circuit as well.

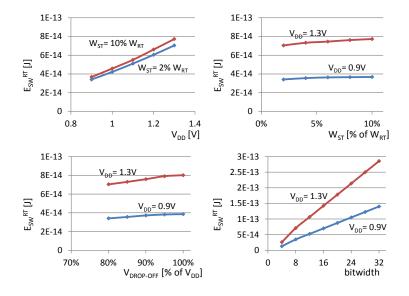

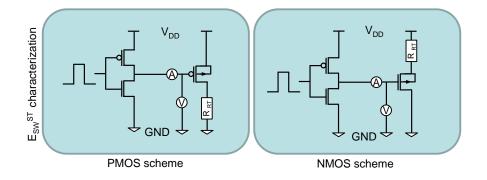

**Transient wake-up state** At the beginning of this phase a falling edge occurs at the sleep signal and thus the sleep transistor conducts. The capacitances within  $c_1$  are loaded and a high current is drawn during wake-up. The wake-up time that is necessary to obtain the steady active state with a virtual supply voltage close to  $V_{DD}$  is denoted as  $t_{wakeup}$ . During wake-up, the maximum current is limited to  $I_{ON}$  of the sleep transistor. The overall consumed energy due to capacitance charging is denoted as state transition energy  $E_{SW}^{RT}$  as defined in Equation 2.5.

$$E_{SW}^{RT} = \int_{t_{wakeup}} V_{DD} \cdot I_1(t)$$

(2.5)

The previous trace is only slightly different for NMOS power-gating and all previous discussions are applicable for footer cells as well. Obviously, *sleep* needs to be inverted. The most important difference regards the voltage levels that appear. In active state, the voltage across the circuit is again close to  $V_{DD}$  with a small IR drop across the sleep transistor. The circuit node between sleep transistor and circuit is now denoted as virtual ground with a voltage of VGND. During power down the circuit again continues to leak but this time the circuit's internal nodes saturate at  $V_{DD}$ . Defining  $I_1$  as the current flowing through the sleep transistor, the  $E_{SW}^{RT}$ -definition holds for header- as well as footer-based power-gating.

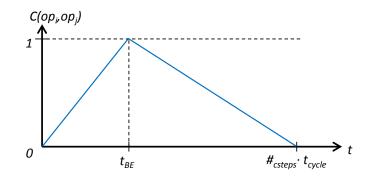

### **Profitability of Power-Gating**

If a sleep phase of a circuit is long enough to amortize the state switch costs, power-gating is a disbursing technique. With the definition of state transition energy in Equation 2.5 and known leakage currents in active and sleep state ( $I_{ACTIVE}$  and  $I_{SLEEP}$ ) a break-even time  $t_{be}$  can be computed. Regrettably, some further costs occur that need to be considered in the  $t_{be}$  computation. For example, the header or footer transistor, necessary interfacing circuits, or buffers (the latter two will be described in Section 2.2.3) have inherent leakage currents and consume an inherent amount of energy during state transition. Thus,  $t_{be}$  is

defined as shown in Equation 2.6 with  $E_{OVERHEAD}$  and  $I_{OVERHEAD}$  summing up all additional energies and currents respectively.

$$t_{be} = \frac{E_{SW}^{RT} + E_{OVERHEAD}}{\left(I_{ACTIVE} - \left(I_{OFF} + I_{OVERHEAD}\right)\right) \cdot V_{DD}}$$

(2.6)

In Chapter 4 the overhead energies and additional currents will further be quantified.

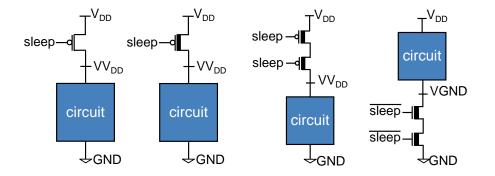

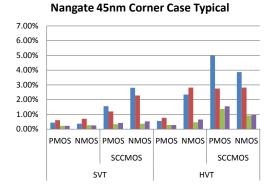

## 2.2.1 Microarchitectural Implementation of Power-Gating

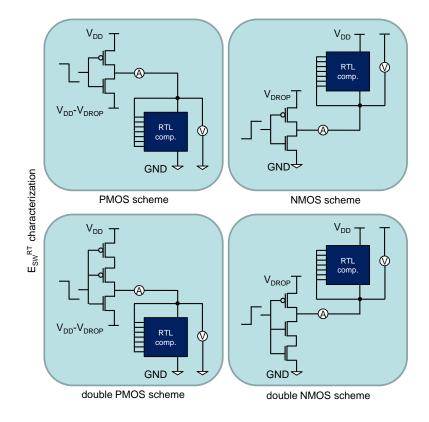

Figure 2.5 shows some exemplary types of microarchitectural implementations of power-gating. Each of these possible implementations is referred to as power-gating scheme (PGS) in the subsequent part of this thesis. In general, the first three schemes apply p-channel metal-oxide semiconductor (PMOS) gating whereas the last scheme implements NMOS gating. For powering down, PMOS sleep transistors are driven by a signal *sleep* equal to the supply voltage whereas NMOS transistors are driven by the inverse signal  $\overline{sleep}$ . In the first scheme, a PMOS transistor that is built in a standard threshold voltage (SVT) process is used for powering down the circuit. The power-gated circuit is typically also made of SVT transistors to provide highest possible performance. This kind of power-gating implementation, also referred to as cutoff CMOS (CCMOS), is nearly outdated, but is considered in this thesis for the sake of completeness. The second scheme implements an HVT sleep transistor (indicated by the thick channel) to maintain a higher potential at the virtual rail and thus to push the suppression of leakage currents. Another advantage of HVT sleep transistors is a reduced inherent leakage current of the transistor itself being relevant because of its size as described in Section 2.2.2. A combination of HVT sleep transistors and SVT circuit is state-of-the-art in today's realization of power-gated designs. For this reason, power-gating is also often referred to as multiple threshold CMOS (MTCMOS) in literature although multi-threshold CMOS only indicates the availability of devices with different threshold voltages, typically a low and a high threshold device. [RMMM03] gives an overview on possibilities how different threshold voltages can be obtained during manufacturing either by body biasing or gate engineering.

Figure 2.5: Microarchitectural implementation of different power-gating schemes

To enforce the leakage suppression, the *sleep* input of a PMOS transistor can be driven by voltage values above  $V_{DD}$ . In literature, this technique is referred to as super cutoff CMOS (SCCMOS) [KNS00].

A problem that arises in doing so is a high voltage  $V_{GD}$  between the *gate-* and *drain-*terminal of the sleep transistor. This leads to a high voltage stress that may even result in a gate oxide breakdown of the transistor. To overcome this problem the third power-gating scheme applies two sleep transistors in series. A SCCMOS implementation then drives the supply-facing device with a sleep voltage above the supply voltage and the circuit-facing transistor with the supply voltage. Then, a voltage level arises between the two sleep transistors that is uncritical regarding the gate-to-drain voltage of the supply-facing transistor [MS02]. The transistor stack further leads to a higher voltage drop across the transistors in both, the sleep and active state. This will better suppress the leakage currents during sleep but will also further reduce the virtual supply voltage and thus the speed during operation.

Every PMOS gating scheme has a corresponding NMOS gating based counterpart. For example, the fourth scheme shown in Figure 2.5 is the NMOS gating counterpart of the one before. NMOS gating has significant advantages compared to PMOS gating because the on-current  $I_{ON}$  is about twice as high if the transistors are of the same size. Thus, an NMOS sleep transistor has less impact on the active state and on the state transition or can be smaller at the same performance.

Beside the sleep transistor selection, other critical design considerations exist in order to optimally power-gate. [SH06b, SH06a] summarize and trade off header vs. footer cells, grid vs. ring style placement and analyzes the sleep transistor efficiency based on gate length, width, and body voltage.

All mentioned techniques have in common that the saturated voltage level equalizes to either  $V_{DD}$  in NMOS case (and GND in PMOS case respectively) for the whole power-gated circuit. Thus, during wake-up of a PMOS gated circuit all nodes of the pull-up network conduct simultaneously. After a while, the voltage is close to  $V_{DD}$  and a big fraction of the pull-up network stops conducting. The circuit ripples until a steady state, defined by the inputs, is obtained. A specialized form of power-gating called zigzag SCCMOS (ZSCCMOS) can reduce this unnecessary dynamic power due to the rippling for a fixed and predefined state during power down [MS02]. PMOS and NMOS sleep transistors are mixed in this approach according to the input values of a gated circuit. For example, an inverter with a logic one as input is PMOS gated because then the virtual supply voltage level saturates to a voltage level above GND and even if high cutoff voltages are applied (see SCCMOS) the sleep transistor is not subjected to a high voltage stress. During wake-up, the capacitances are already precharged and much less power is consumed. In turn, this technique is not as powerful in reducing leakage currents because of its fine-grained application.

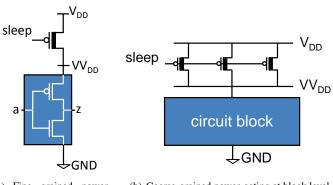

## 2.2.2 Granularity of Application

Beside the scheme of power-gating implementation, another important aspect is its granularity of application in both spatial as well as temporal meaning.

Spatial granularity considers the circuit size to be powered down. Approaches presented in literature range from fine-grained techniques with dedicated sleep transistors for each gate of a technology up to coarse-grained techniques where large IP components are power-gated via a single sleep transistor or a cluster of parallel sleep transistors. In the following, the pros and cons will be explained.

**Fine-grained spatial power-gating** duplicates every cell in the standard cell library and adds a single sleep transistor [KS04] as it is shown for an inverter cell in Figure 2.6(a). Thus, a fine-grained power-gating compatible technology typically contains twice as many cells. The sleep transistor size is individ-

(a) Fine grained power- (b) Coarse-grained power-gating at block level gating at gate level

Figure 2.6: Spatial granularity of power-gating

ually matched to the gated cell and is fixed in the library. Thereby, sizing depends on the  $I_{MIC}$  drawn during active state. This highly decentralized approach implies some advantages. First of all, the timing and delay information can be analyzed during library characterization and thus be stored in the library files such as in the liberty file format. The same holds for the layout as every cell's layout is fixed and the area overhead is known. As no separate sleep transistors are required, the effort for placement will not be increased. The third advantage of the fine-grained approach is a compatibility with existing design tools and thus its seamless integration in existing tool flows. On the other hand, the huge number of sleep transistors implies some disadvantages. Since every sleep transistor needs to be controlled, the sleep signal distribution demands a high effort during interconnect routing. Secondly, every sleep transistor should be properly sized for its gate. Beside the pessimistic sizing for  $I_{MIC}$ , the lower bound for transistor width is limited by the technology size. From a global perspective this will lead to a far pessimistic design and thus a large area penalty. Additionally, the efficiency of power-gating is limited as already shown in the NAND-gate example of Figure 2.3 for small gates because the relation between  $I_{OFF}^{ST}$  and  $I_{ON}^{Gate}$  is too big. This effect will become even worse for smaller gates. Moreover, the library complexity is increased due to the number of gates and annotated timing information.

Approaches powering down more than a single gate by one or multiple sleep transistors connected in parallel are referred to as **coarse-grained spatial power-gating** techniques. They can further be divided into *cluster based sleep transistor design (CBSD) techniques* where each cluster of few gates has its own sleep transistor and *distributed sleep transistor network (DSTN) based design techniques* where several sleep transistors are shared to power down larger circuit parts [LH04] and are coarsely placed throughout the chip. Sharing means that there is one virtual supply or ground line among the sleep transistors. In today's industrial power-gating designs, DSTN design is state-of-the-art [SLJY08]. Figure 2.6(b) exemplarily shows a circuit block powered down by three shared sleep transistors.

In these approaches only a few header or footer cells of different sizes are added to the library (as presented in [CPS<sup>+</sup>07] for a 65nm technology node) and are characterized separately from the powergated circuit. Due to the linear proportionality between  $W_{ST}$  and  $I_{ON}$  (and  $I_{OFF}$  respectively) they are then combined in order to meet the target size. Other advantages of the coarse-grained application arise from the sharing of sleep transistors. On the one hand the sleep control distribution is much easier. On the other hand the area overhead can be reduced significantly because the sleep transistors share the virtual supply or ground line and the  $I_{MIC}$  of a large circuit block is much lower than the aggregated maximum currents of its individual parts. Additionally, it is less sensitive to process-voltage-temperature (PVT) variation and, if the distributed sleep transistors are sized properly, it introduces less IR drop variation [SH06a]. But the sleep transistor size is also the main problem of this approach because it is now a parameter of the design trading off area overhead and timing degradation. Another drawback is the lack of electronic design automation (EDA) tool support for sleep transistor sizing and synthesis of power-gateable circuits.

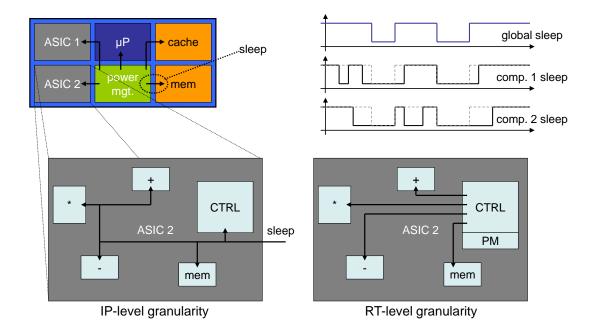

Figure 2.7: Temporal granularity of power-gating application

Within the class of coarse-grained spatial power-gating approaches an additional separation can be made when ASIC hardware is considered. Simple approaches only power-gate ASIC designs as a whole whereas more sophisticated approaches look into it and power down at register transfer (RT) level basis. Figure 2.7 compares these two possibilities. In the first implementation the ASIC does not contain power-management functionalities and is entirely controlled from outside via a global sleep signal. Shorter idle times of single RTL components are neglected. In the example shown, the sleep signal is distributed to every included RTL component everyone having its own power down mechanism. Alternatively, it could also be implemented in a way that the overall ASIC is powered down by a single power switch. In the second version, the ASIC's internal controller is extended by power-management functionalities. It either observes the workload or knows by its controller-states when RTL components can be put into sleep mode. This approach is more flexible as single RTL components such as adders or multipliers can be powered down for few cycles on an individual basis. This is especially an advantage if the workload-traces vary between components.

Of course, these two approaches can be combined in order to apply an autonomous control within the ASIC as well as providing the possibility for a global power down.

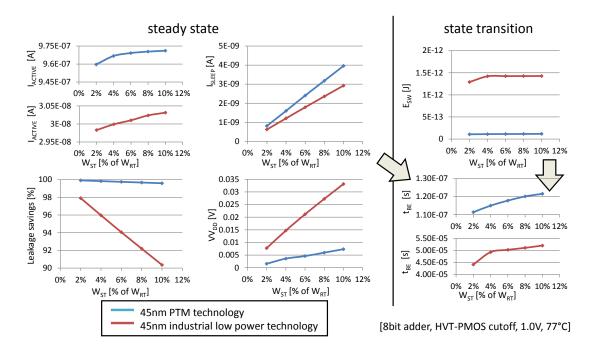

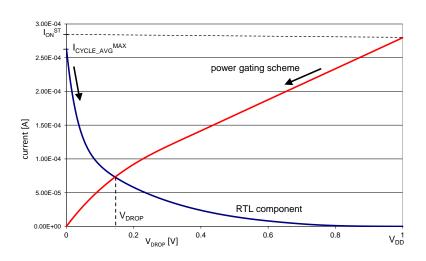

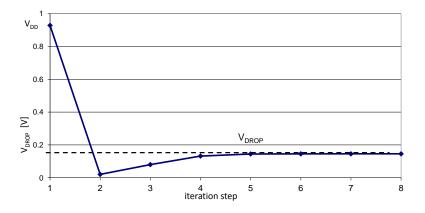

In all cases, the break-even time to amortize the state transition costs decides which granularity is the most suitable. Figure 2.8 shows break-even time computations based on measured  $I_{ACTIVE}$ ,  $I_{SLEEP}$ , and  $E_{SW}^{RT}$  curves. The measurements have been performed by Synopsys HSPICE<sup>®</sup> simulations powering down an 8-bit adder by PMOS gating with a supply voltage of 1.0V assuming an operating temperature of 77°C. Two transistor technologies have been examined: the Nangate free 45nm open source digital cell library based on the predictive technology model (PTM) and an industrial 45nm low power technology. The sleep transistor width remained a parameter as indicated in the charts. The subsequently break-even time computation has been performed as defined in Equation 2.6.

The results clearly show the  $t_{be}$  sensitivity regarding different technologies. While the break-even time of the PTM technology ranges between 110 - 122ns what is equal to about 12 cycles at a 100Mhz clock speed, it is significantly higher for the industrial 45nm technology. Thus, a temporal fine-grained power down at RT level only makes sense for the PTM technology. In [SSCS10] the authors analyze the break-even time of several larger circuits implemented in an older and less leaky 65nm technologies to be in the order of one  $\mu s$ . This result underlines a sophisticated analysis of an application of power-gating.

Figure 2.8: Break-even time computations of power-gating application

## 2.2.3 Interfacing to Power-Gated Circuits

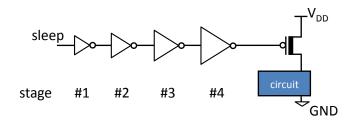

Communicating with a power-gated circuit is a critical issue. First of all, the sleep signal that is typically provided by a controller needs to be lead to the sleep transistor in a sufficient strength. This is important because the spatial distance between sleep transistor and controller on the chip might be big and only small wires should be used for long distances due to the wire load. On the other hand, the sleep transistor size might be significantly larger compared to a standard transistor and thus a high drive is necessary to load its gate capacitance and obtain reasonable switching performance. For these reasons, a cascaded buffer chain is inserted in front of the sleep transistor input in order to stepwise amplify the sleep signal. Figure 2.9 shows such a stepwise tapered buffer chain. The buffers grow rate is the main characteristic to differentiate approaches in literature. It has been shown that an exponentially tapered buffer (i.e. with a ratio of e) provides the minimum system delay [JL75]. Every buffer in the chain thus has an input capacity that is e-times as large as the output capacity of the predecessor. More sophisticated approaches even take the local interconnect capacities between two consecutive stages into account and compute individually sized buffers [CF95a, CF95b, PPD<sup>+</sup>98], delay-optimized [Bla96], or energy minimizing tapering factors [KAP03]. In practice, buffer sizing also depends on the availability of inverter standard cells.

Figure 2.9: Stepwise buffer tapering

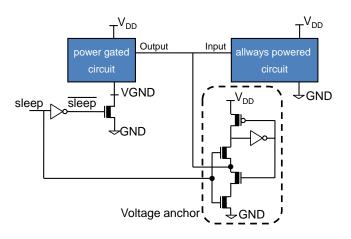

Secondly, data outputs of a power-gated circuit need to be isolated because they tend to float at intermediate potentials and cause large short-circuit currents in the subsequent circuit. For this purpose, voltage anchors have been introduced that pull the output voltage up or down to a legal value immediately before the sleep signal is raised. Voltage anchors are small devices and thus introduce a small area overhead of 6 to 14 minimally sized transistors [BBMM06]. An exemplary voltage anchor, forcing the output to the latest value, is shown in Figure 2.10. The voltage anchor activation is derived directly out of the sleep signal that is delayed and then used to power down the circuit.

In contrast to the data output, the inputs of a power-gated circuit are less critical and do not need to be handled carefully. Of course, they have an impact on the saturating voltage but no voltage anchors are needed since they cannot cause short circuit currents or a state-loss.

## 2.2.4 Advanced Concepts

As shown above, the main limitations for applying power-gating are the high state transition costs and the state-loss after a short time in the gated state.

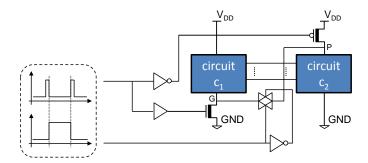

To overcome the high dynamic power during a state transition, the concept of charge recycling has

Figure 2.10: Exemplary voltage anchor holding the latest output value [BBMM06]

been proposed [PFP08]. It introduces a transmission gate (TG) as a charge sharing switch between the virtual supply of one and the virtual ground of another power-gated circuit. The approach requires a zigzag-application of power-gating with alternating NMOS and PMOS gating. In the constellation shown in Figure 2.11, the potential at G is very close to  $V_{DD}$  and at P it is very close to GND. Immediately before a rising edge occurs at the sleep signal, the TG closes for a short time and the potentials at G and P align each other. In this moment a part of the charged energy in  $c_1$  is transferred to  $c_2$  reducing the transition costs for both circuits.

Figure 2.11: Charge-recycling for power-gated circuits [PFP08]

An energy saving analysis showed a reduction of transition energy up to 43% while the wake-up time is maintained. Additionally, this approach has a positive impact on the peak voltage drop and it reduces the ground bounce during wake-up. Nevertheless, this technique also introduces additional costs in terms of area for the TG.

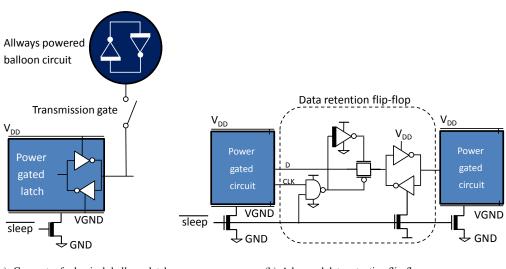

Secondly, to overcome the state-loss of memories during power-gating, balloon latches have been introduced [SMM<sup>+</sup>97] for state retention. A balloon circuit, as shown in Figure 2.12(a), contains two additional coupled inverters that are always powered on and take over the state from a standard latch or flip-flop via a transmission gate before powering down. During wake-up, the state is restored. While the

(a) Concept of classical balloon latch (b) Advanced data-retention flip-flop based data retention

Figure 2.12: Different data retention techniques

memory element that should be powered down is implemented in the SVT process, the balloon latch is made of HVT devices, thus the difference in their leakage current is saved during sleep state.

In [MMR04], an even more advanced concept for data-retention is proposed. Figure 2.12(b) shows a data-retention flip flop with properly gated clock and data inputs that holds its state even during sleep mode. The internal clock and data gating needs to be powered on always in order to prevent a change of the stored data in the coupled transistors. By applying data-retention techniques to all state-containing memories, the overall datapath can be powered down and the level of granularity can be raised from RTL-wise gating to system-level gating.

Another possibility to prevent a state-loss is to clamp the virtual supply or virtual ground voltage within the power-gated design. This is done by inserting rail clamp devices such as diodes [KIY<sup>+</sup>98], additional PMOS devices as diode [KKS04], or by a clever interconnect of the sleep transistor driving buffer [TNN06]. In all of these cases, the falling  $VV_{DD}$  or rising VGND is limited to a state-preserving value.

A very new field of research is to find alternative power switches like microelectromechanical systems (MEMS) [HN10]. MEMS are physical levers that bend due to any kind of electrostatic, piezoelectric, thermal, or magnetic force and thus form a bonding. They are optimal switches because they cause negligible voltage drops, do not leak inherently and, due to the physical void, the standby leakage is zero. Drawbacks of MEMS are the large switching time of about  $100\mu s$  and the complex integration into CMOS circuits.

In [WC10], spintronic memristors are proposed for use as power-gating switches. Memristors are variable resistors that depend on an integral of the current/voltage profile. To actively power control a circuit with a memristor connected in series, its memristance needs to be increased significantly. This will occur after a certain amount of energy that has been drawn. Due to the lack of external controllability, memristor switches can only be used in special cases such as power budgeting.

## 2.2.5 Summary

Although significant improvements in transistor design have been made, leakage remains a limiting factor in the *smaller*, *faster*, *and less power* mentality of today's semiconductor development. As shown, powergating is **the** upcoming and seldom already applied technique to control leakage currents. It outperforms any other leakage reduction technique by far but for an automated use in the design of ASIC designs, still several design challenges exist:

- · Choice of power-gating implementation scheme,

- Placement and sizing of sleep transistors,

- Automated generation and distribution of sleep signals,

- Sleep signal scheduling for wake-up noise reduction (ground bounce reduction),

- Mode transition energy  $(E_{SW}^{RT})$  minimization, and

- State retention issues.

Today, coarse-grained MTCMOS approaches are state-of-the-art as they can be applied to existing IP. The most important drawback is the need for large sleep times to amortize the costs. In contrast, fine-grained MTCMOS is much easier to implement but offers only a limited leakage reduction. Thus, the future of power-gating will be in between a coarse- and fine-grained application to overcome these limitations. In all cases, many aspects need to be considered for creating models and to optimize designs for power-gating. Solutions to overcome the main problems exist or will be proposed in this thesis and can jointly be applied.

Worth reading summaries of the principles, history, and especially technical implementation details of power-gating techniques are also presented in [Hen07] (Chapter 5) and [SSCS10].

# 2.3 High-Level Synthesis

Rising design complexity, reuse of design entities, and the need for effective design tradeoffs force the demand for an automated synthesis. Within the process of an HLS (also referred to as *behavioral synthesis* and *algorithmic synthesis*) a formal specification of an algorithmic behavior is synthesized/compiled to hardware in terms of a fully timed microarchitectural description that implements that behavior. The HLS output can then directly be forwarded to conventional logic synthesis with an existing tool support of more than 25 years<sup>1</sup>.

First generation HLS tools such as Synopsys<sup>®</sup>'s *Behavioral Compiler* based on behavioral Verilog or VHDL for design description but have not established because of the languages' insufficiency in modeling a behavior as well as the partial timing abstraction. Today's HLS tools base on standard languages such as ANSI C/C++ or SystemC for modeling behaviors.

Several hopes are related with an automated translation. Hardware could be built more efficiently, optimizations techniques can be adopted automatically, and design-space explorations can be examined

<sup>&</sup>lt;sup>1</sup>Parts of the Synopsys<sup>®</sup> Design Compiler, being the first logic synthesis tool, can be dated back to 1986.

for any of the design targets area, performance, power (dynamic as well as static), and reliability. Beside these investigations, a verification of the hardware against its behavior is another important aspect of an HLS.

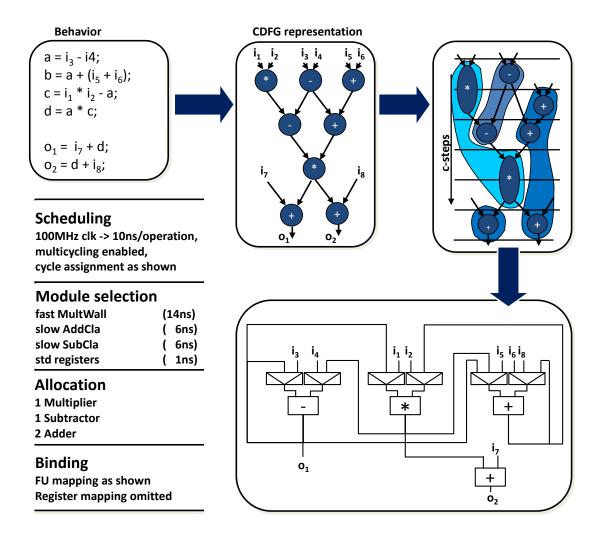

In general, an HLS consists of the following activities that can be implemented in different orders and with different algorithms:

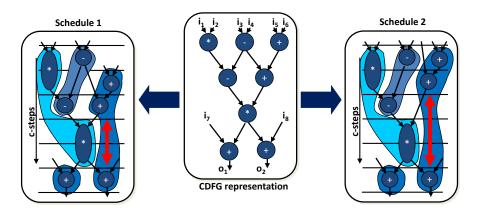

- Lexical processing for representing the behavioral description in a graph notation. Typically, a control- and data-flow graph (CDFG) is used that combines a *data-flow* with a *control-flow*-graph. Thus, nodes represent either functional operations (+,- or \*) or control-flow nodes (e.g. split or join) and edges represent either directed data flows (e.g. the output of an adder operation defines an input of a subsequent multiplication) or control edges expressing the successor relation in a sequential program flow.

- Algorithmic optimization can be performed onto the graph. For example, loops can be unrolled or merged and the number of stages in a filter design can easily be changed.

- **Data/Controlflow analysis** examines data- and controlflow-dependencies between the CDFG nodes. For example, unused variables can be identified by static analysis techniques and data dependencies may be removed to relax the total amount of constraints.

- **Resource allocation** constrains the number of each functional unit available in the subsequent synthesis phases and to be used in the microarchitectural datapath.

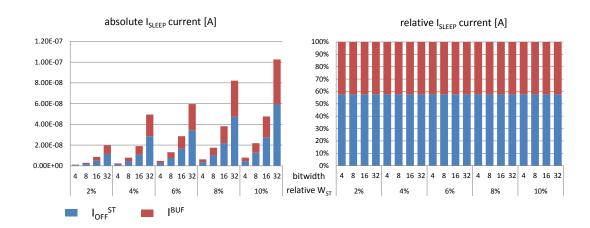

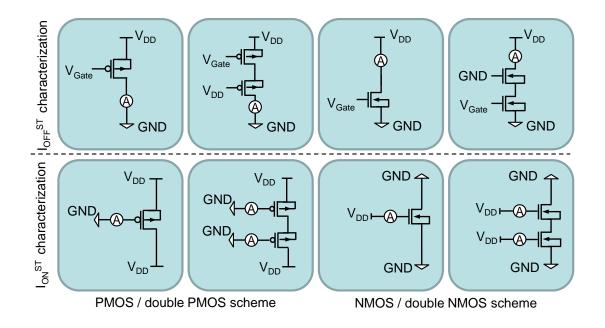

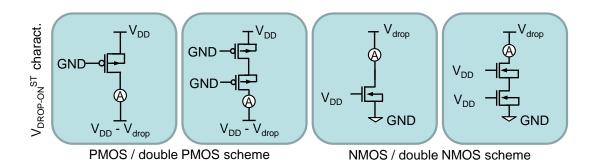

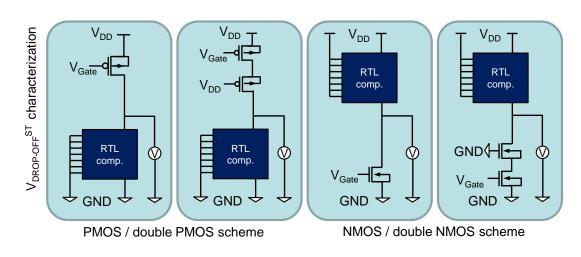

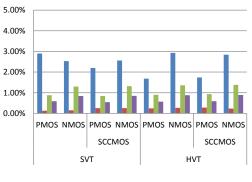

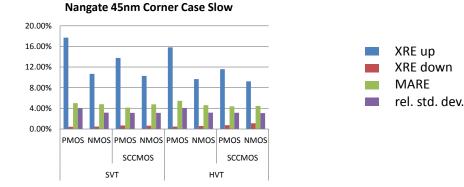

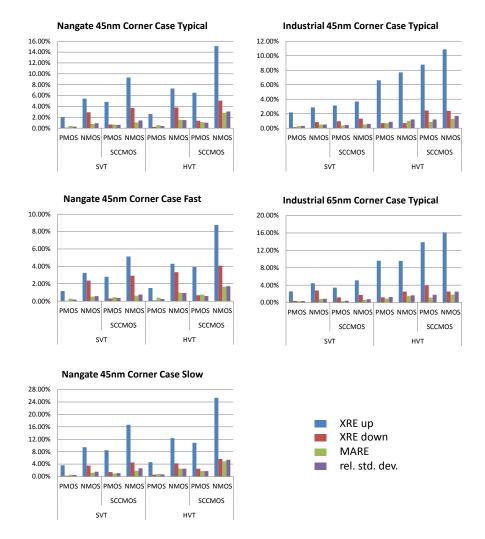

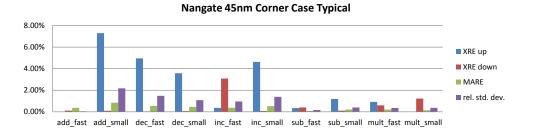

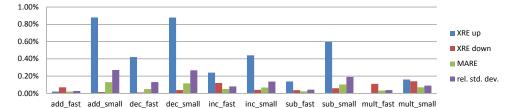

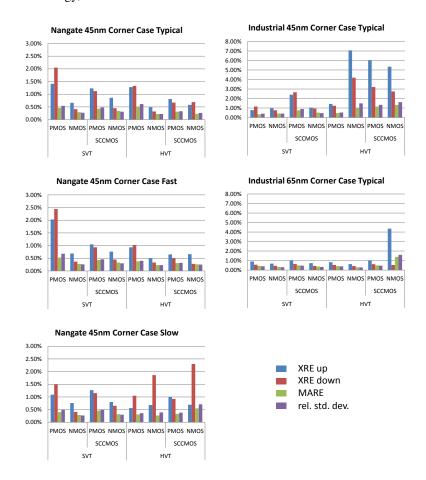

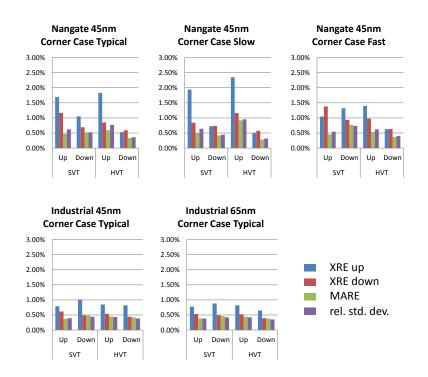

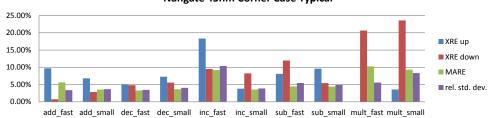

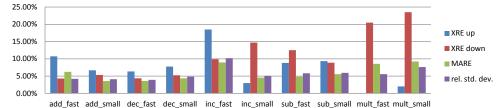

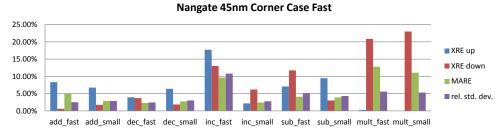

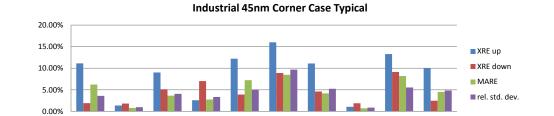

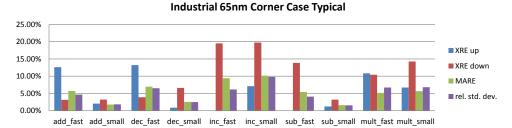

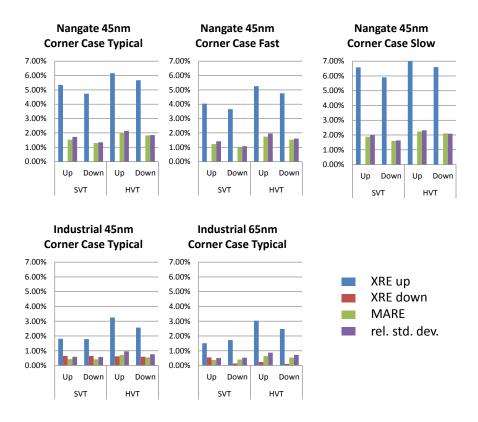

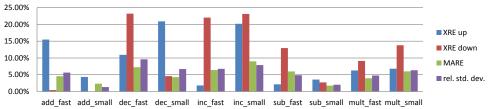

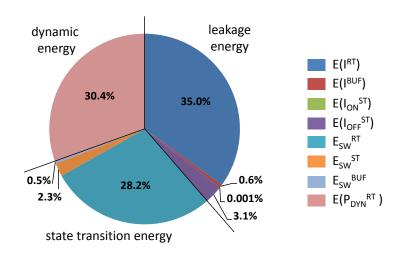

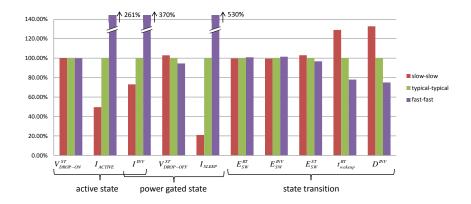

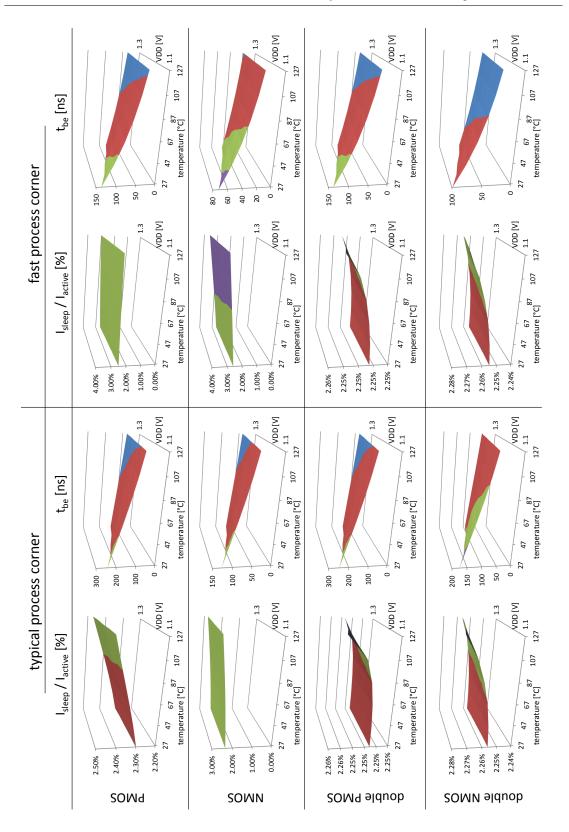

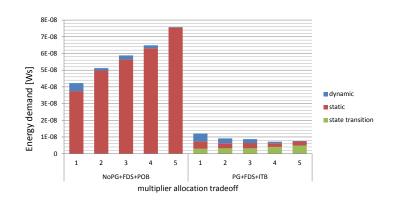

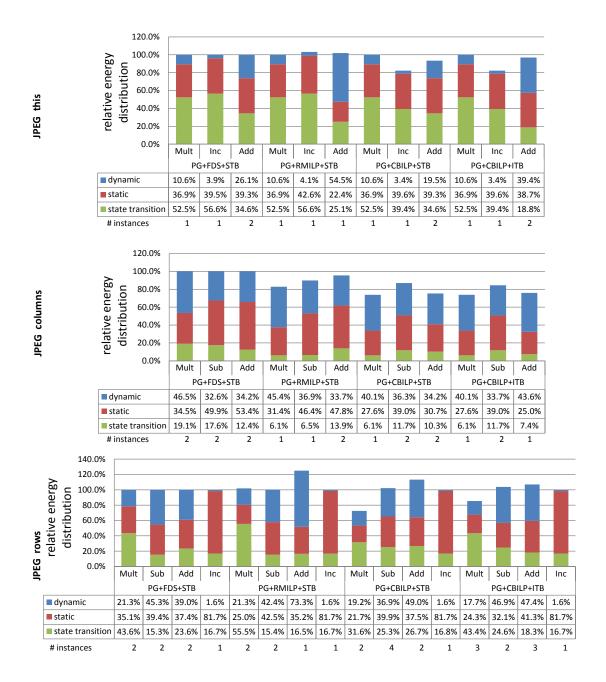

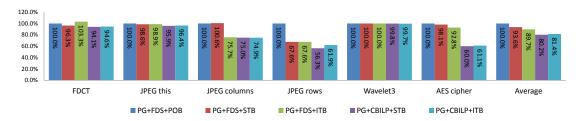

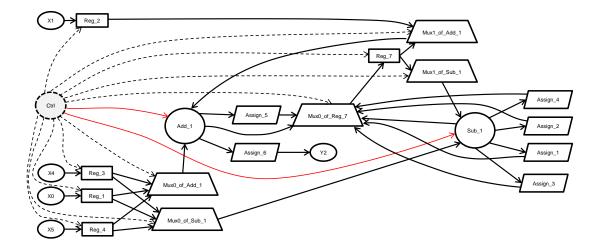

- **Module selection** decides on different implementation alternatives of a functional unit (FU). For example, different types of digital adders exist such as ripple carry, carry-lookahead, or carry-save adder. Furthermore, each component may exist in different variants such as in a fast or small version in order to satisfy precise demands.