## Verification Architectures for Complex Real-Time Systems

Dissertation zur Erlangung des Grades eines Doktors der Naturwissenschaften

vorgelegt von

Dipl.-Inform. Johannes Faber

Oldenburg, 19. April 2011

Gutachter:

Prof. Dr. E.-R. Olderog Prof. Dr. B. Finkbeiner (Uni Saarbrücken)

Datum der Einreichung: 19.04.2011 Datum der Verteidigung: 29.08.2011

ⓒ 2011 by the author

Author's address: Johannes Faber Fakultät II, Department für Informatik Abteilung "Entwicklung korrekter Systeme" 26111 Oldenburg Germany

E-mail: johannes.faber@informatik.uni-oldenburg.de

For my loved girls Melanie & Elyenna

### Abstract

In the analysis of complex real-time systems, several aspects have to be covered, e.g., behaviour that conforms to communication protocols, rich data structures, and timing constraints such that the system reacts timely to external events. In practise it turns out that to handle such systems engineers fall back on combinations of techniques. An example is the Unified Modelling Language, combining multiple graphical notations for different views of a design. Similarly, in the world of formal analysis there has been a lot of work on integrating specification techniques to condense advantages of single formalisms into combined formalisms. However, a major problem remains: these integrated techniques are designed for heterogeneous systems, and when formally verifying those systems, one has to cope with their inherent complexity.

To solve this problem, we propose to verify global properties by combining local analyses using abstract, behavioural protocols. This idea originates from previous case studies, where a specification of the European Train Control System is decomposed according to a behavioural protocol. The protocol splits the system runs into several phases with local real-time properties which hold during these phases. After showing the correctness of a desired global safety property, this property is also guaranteed by all instances of the protocol that fit to the structure of the protocol and satisfy all local properties. We generalise and formalise this approach in a uniform framework for combined real-time formalisms.

As several combined specification formalisms are based on Communicating Sequential Processes (CSP), we introduce a CSP extension to specify system protocols with data and unknown processes to capture a large class of systems. On the unknown processes, local real-time assumptions are specified by formulae in an arbitrary logic. By this means, a decomposition of a global property into local assumptions on protocol phases is defined. We call these protocols with local real-time assumptions *Verification Architectures (VA)*. To establish safety properties on VAs, we embed the CSP extension into a temporal dynamic logic and introduce a sound sequent-style proof calculus. We prove that all models that structurally refine the CSP part of a VA and that satisfy the real-time assumptions inherit the desired properties.

The instantiation of VAs is exemplified with a combined formalism, called CSP-OZ-DC. The real-time logic Duration Calculus is used to specify assumptions on protocol phases. We introduce a syntactical proof rule to show efficiently that a CSP-OZ-DC specification structurally refines a VA protocol. The correctness of the assumptions is shown by using an existing model checking approach. Furthermore, by presenting a case study from the European Train Control System, we demonstrate the verification of a complex real-time system with the VA approach.

### Zusammenfassung

Für die Analyse komplexer Realzeitsysteme sind verschiedene Faktoren relevant und müssen berücksichtigt werden. Dazu gehören unter anderem Kommunikations- und Kontrollflusseigenschaften, die verwendeten Datenstrukturen und das zeitliche Verhalten des Systems. Um diese heterogenen Aspekte umfassend beschreiben zu können, hat es sich in der Praxis durchgesetzt, Kombinationen von Analysetechniken zu verwenden. Ähnliches gilt für die formale Analyse und Verifikation von Realzeitsystemen, für die ebenfalls verschiedene formale Techniken kombiniert werden. Da diese Systeme, die mit kombinierten Techniken untersucht werden, inhärent komplex sind, gerät die formale Analyse an die Grenzen ihrer Möglichkeiten – es müssen Wege geschaffen werden, die Komplexität der Systeme zu reduzieren.

Aus diesem Grund wird in dieser Arbeit ein Ansatz vorgeschlagen, der die Analyse globaler Systemeigenschaften auf lokale Eigenschaften reduziert. Dies geschieht mit Hilfe von formalen Entwurfsmustern, die abstrakte Protokolle für bestimmte Systemklassen beschreiben. Die Protokolle unterteilen Systemabläufe in verschiedene Phasen, für die Realzeiteigenschaften als Annahmen vorausgesetzt werden. Wenn gezeigt werden kann, dass das Protokoll gewünschte Sicherheitseigenschaften gewährleistet, dann gelten diese Eigenschaften für alle Instanzen des Protokolls; dazu müssen Struktur von Instanz und Protokoll übereinstimmen und die lokalen Realzeiteigenschaften nachgewiesen werden. In dieser Arbeit wird dieser Ansatz mit Fokus auf kombinierte Spezifikationstechniken untersucht.

Da verschiedene kombinierte Formalismen auf der Prozessalgebra Communicating Sequential Processes (CSP) basieren, wird eine Erweiterung von CSP um Daten und unbekannte Prozesskomponenten vorgestellt, mit der abstrakte Systemprotokolle mit großem Freiheitsgrad beschrieben werden können. Für die unbekannten Prozesskomponenten können Realzeitannahmen in einer beliebigen Logik definiert werden. Da sich auf diese Weise globale Eigenschaften des Protokolls in lokale Annahmen zerlegen lassen, werden solche Protokolle als *Verifikationsarchitekturen (VA)* bezeichnet. Um globale Eigenschaften von VAs nachweisen zu können, werden eine Einbettung der CSP-Erweiterung in Dynamische Logik und ein Sequenzenkalkül für diese Logik präsentiert.

Die Instanziierung von VAs wird exemplarisch für die kombinierte Sprache CSP-OZ-DC gezeigt, indem eine Beweisregel für einen syntaktischen Verfeinerungsnachweis eingeführt wird. Die Korrektheit der lokalen Eigenschaften wird mit existierenden Model-Checking-Verfahren gezeigt.

Abschließend wird mit Hilfe einer Fallstudie über das Europäische Zugkontrollsystem belegt, dass der VA-Ansatz geeignet ist, komplexe Realzeitsysteme zu verifizieren.

## Contents

| 1. | Intro | duction                                                      | 1         |

|----|-------|--------------------------------------------------------------|-----------|

|    | 1.1.  | Running Example: A Small Train Control System                | 5         |

|    | 1.2.  | Overview of the VA Approach                                  | 6         |

|    | 1.3.  | Related Work on Pattern-Based and Compositional Verification | 8         |

|    | 1.4.  | Structure of this Thesis                                     | 1         |

|    | 1.5.  | Acknowledgements                                             | 2         |

| 2. | Prel  | ninaries 1                                                   | 3         |

|    | 2.1.  | CSP, OZ, and DC                                              | 4         |

|    |       |                                                              | 4         |

|    |       |                                                              | 7         |

|    |       |                                                              | 22        |

|    | 2.2.  |                                                              | 26        |

|    | 2.2.  |                                                              | 28        |

|    |       |                                                              | 80        |

|    |       |                                                              | 32        |

|    | 2.3.  | **                                                           | 3         |

|    | 2.0.  |                                                              | 3         |

|    |       |                                                              | 8         |

|    |       |                                                              |           |

| 3. | Exte  | ded CSP for Verification Architectures 4                     | 1         |

|    | 3.1.  | CSP Processes for Verification Architectures                 | 2         |

|    |       | 3.1.1. CSP Processes with Data Constraints                   | 3         |

|    |       | 3.1.2. Unknown Processes                                     | 7         |

|    |       | 3.1.3. Assumptions on Unknown Processes                      | 9         |

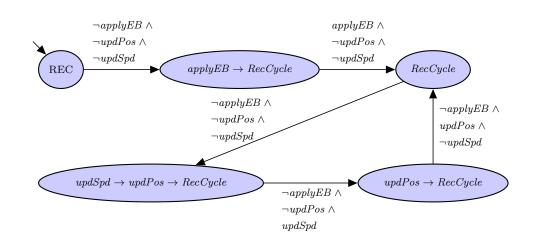

|    |       | 3.1.4. Running Example: A Train Control Protocol             | 50        |

|    | 3.2.  | Properties of Extended CSP 5                                 | 52        |

|    |       | 3.2.1. Continuous CSP Operators                              | 52        |

|    |       | 3.2.2. Discontinuity of Parallel Composition                 | 64        |

|    | 3.3.  | Normal Forms                                                 | 6         |

|    | 3.4.  | Discussion                                                   | 50        |

|    |       | 3.4.1. Parametric Systems                                    | 50        |

|    |       | 3.4.2. Semantics                                             | 51        |

|    |       |                                                              | <b>52</b> |

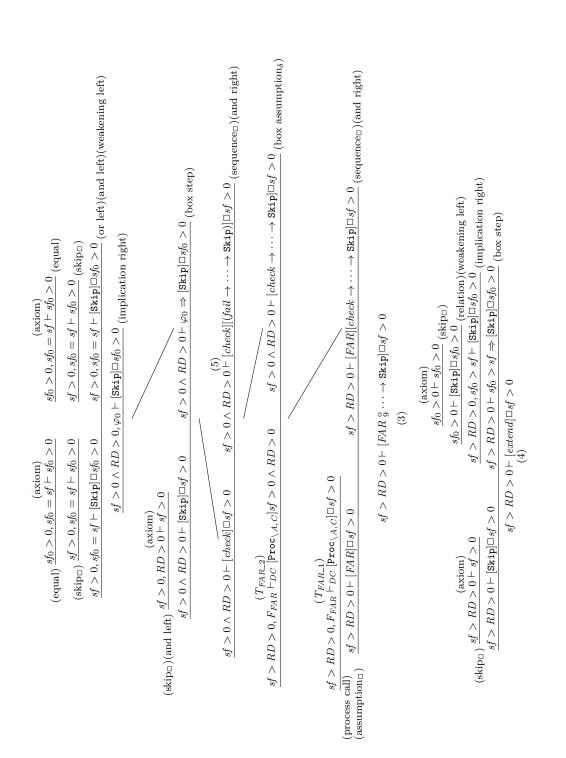

| 4. | A S        | equent Calculus for Verification Architectures                     | 65  |

|----|------------|--------------------------------------------------------------------|-----|

|    | 4.1.       | Dynamic Logic over CSP Processes with Data                         | 66  |

|    | 4.2.       | Sequent Calculus                                                   | 68  |

|    | 4.3.       | Proof Rules                                                        | 70  |

|    |            | 4.3.1. Structural Rules                                            | 70  |

|    |            | 4.3.2. Propositional Rules                                         | 70  |

|    |            | 4.3.3. First-Order Rules                                           | 71  |

|    |            | 4.3.4. Symbolic Execution of dCSP Formulae                         | 72  |

|    |            | 4.3.5. Symbolic Execution of dCSP Specifications with Unknown Pro- |     |

|    |            | cesses                                                             |     |

|    |            | 4.3.6. Induction Rules                                             |     |

|    |            | 4.3.7. Auxiliary dCSP Rules                                        |     |

|    | 4.4.       | Soundness of the Calculus                                          |     |

|    | 4.5.       | 0                                                                  |     |

|    |            | 4.5.1. Checking the Side-Conditions for the Box Operator           |     |

|    |            | 4.5.2. Checking the Side-Conditions for the Diamond Operator       |     |

|    | 4.6.       | Discussion                                                         |     |

|    |            | 4.6.1. Discussion of the VA Approach                               |     |

|    |            | 4.6.2. Related Work                                                | 100 |

| 5. | Refi       | nement of Verification Architectures                               | 105 |

| 0. | 5.1.       | Refinement of Verification Architectures                           |     |

|    | 5.2.       | Simulation of Processes                                            |     |

|    | 5.3.       |                                                                    |     |

|    | 5.4.       | Syntactical Proof Rule for Process Refinement                      |     |

|    | 5.5.       | Property Inheritance                                               |     |

|    | 5.6.       |                                                                    |     |

|    |            |                                                                    |     |

| 6. |            | itations and Extensions                                            | 127 |

|    | 6.1.       | Parallel Unknown Processes                                         |     |

|    |            | 6.1.1. An Automata-Based Semantics for Parallel Unknowns           |     |

|    |            | 6.1.2. Translation-Based Approaches                                |     |

|    |            | 6.1.3. Rely-Guarantee Reasoning for Parallel Unknowns              |     |

|    |            | 6.1.4. Instantiating Parallel Unknowns                             |     |

|    |            | 6.1.5. An Interpretation-Based Semantics for Parallel Unknowns     |     |

|    | 6.2.       |                                                                    |     |

|    |            | 6.2.1. Test Processes for Timing Properties                        |     |

|    | 0.0        | 6.2.2. Extended Calculus for Timing Properties                     |     |

|    | 6.3.       | Examining Completeness                                             |     |

|    |            | 6.3.1. Completeness of VA Language                                 |     |

|    | <b>0</b> 1 | 6.3.2. Completeness of Local Assumptions                           |     |

|    | 6.4.       |                                                                    |     |

|    |            | 6.4.1. Slicing Formal Specifications                               | 170 |

|    |      | 6.4.2. Layered Composition for Timed Protocols                                             | 171 |

|----|------|--------------------------------------------------------------------------------------------|-----|

| 7. | Imp  | ementation and Tools                                                                       | 173 |

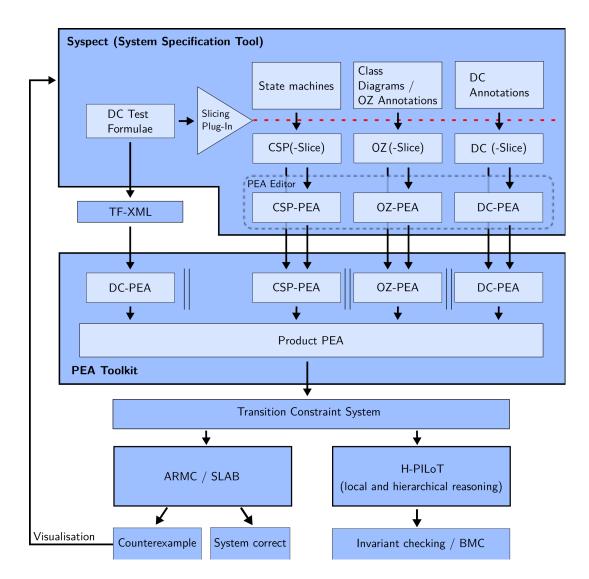

|    | 7.1. | Syspect                                                                                    | 174 |

|    |      | 7.1.1. UML Profile for Real-Time Systems                                                   | 174 |

|    |      | 7.1.2. Tool Structure                                                                      | 178 |

|    |      | 7.1.3. Syspect Plug-Ins                                                                    | 179 |

|    | 7.2. | Verification with Syspect                                                                  | 181 |

|    |      | 7.2.1. Transition Constraint Systems                                                       | 181 |

|    |      | 7.2.2. Verification of Syspect Specifications                                              | 182 |

|    |      | 7.2.3. Slicing CSP-OZ-DC Specifications in Syspect                                         | 185 |

|    |      | 7.2.4. Further Verification Plug-Ins                                                       | 185 |

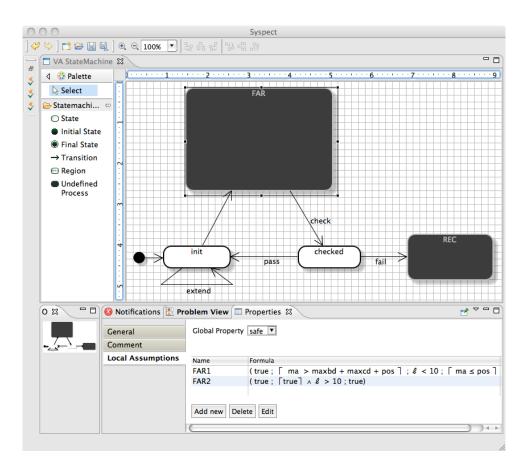

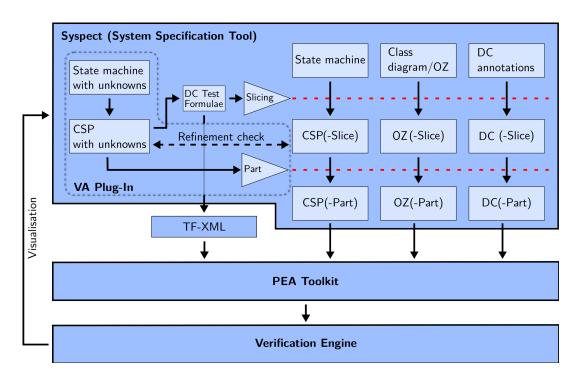

|    | 7.3. | Syspect Verification Architecture Plug-In                                                  |     |

|    |      | 7.3.1. Modelling of VAs                                                                    |     |

|    |      | 7.3.2. CSP-OZ-DC Representation of a VA                                                    |     |

|    |      | 7.3.3. Verification of VAs                                                                 |     |

|    | 7.4. | Discussion                                                                                 |     |

| _  | _    |                                                                                            |     |

| 8. |      | e Studies                                                                                  | 191 |

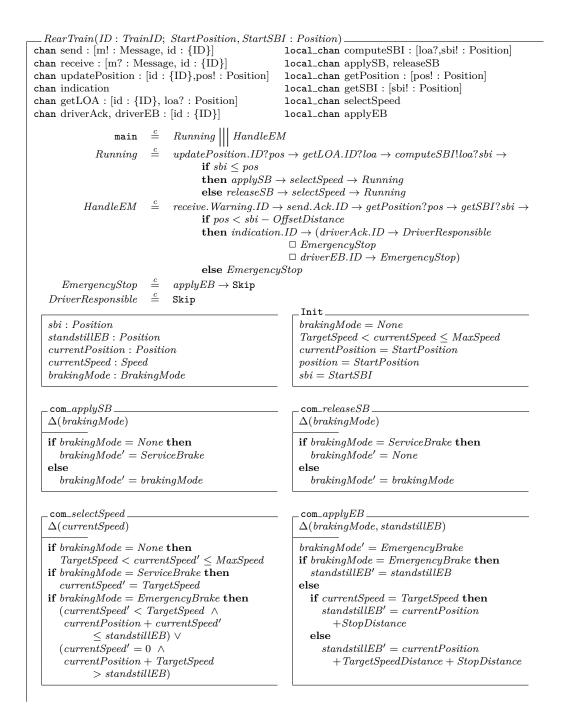

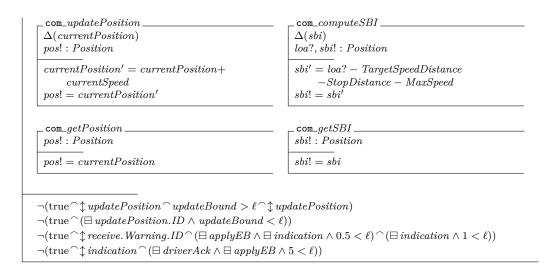

|    | 8.1. | Running Example: Small Train Control System                                                |     |

|    |      | 8.1.1. Verification of the Architecture                                                    |     |

|    |      | 8.1.2. Instantiation by a CSP-OZ-DC Model                                                  |     |

|    | 8.2. | European Train Control System                                                              |     |

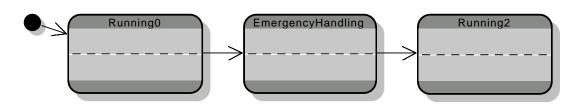

|    |      | 8.2.1. Case Study Scenario: Emergencies in Train Control Systems $\ .$                     |     |

|    |      | 8.2.2. Previous ETCS Case Studies                                                          |     |

|    |      | 8.2.3. VA for the ETCS Case Study                                                          | 202 |

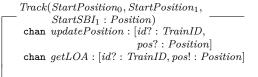

|    |      | 8.2.4. VA Verification                                                                     | 207 |

|    |      | 8.2.5. Instantiating the VA $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 214 |

|    |      | 8.2.6. Checking the Instantiation with Syspect                                             | 216 |

|    |      | 8.2.7. Discussion                                                                          | 220 |

| 9. | Con  | clusions                                                                                   | 223 |

| 5. |      | Discussion                                                                                 | -   |

|    | 9.2. | Alternative Approaches                                                                     |     |

|    | -    | Perspectives                                                                               |     |

|    |      |                                                                                            |     |

| Α. |      | e Study Material                                                                           | 233 |

|    | A.1. | Train Control System of the Running Example                                                |     |

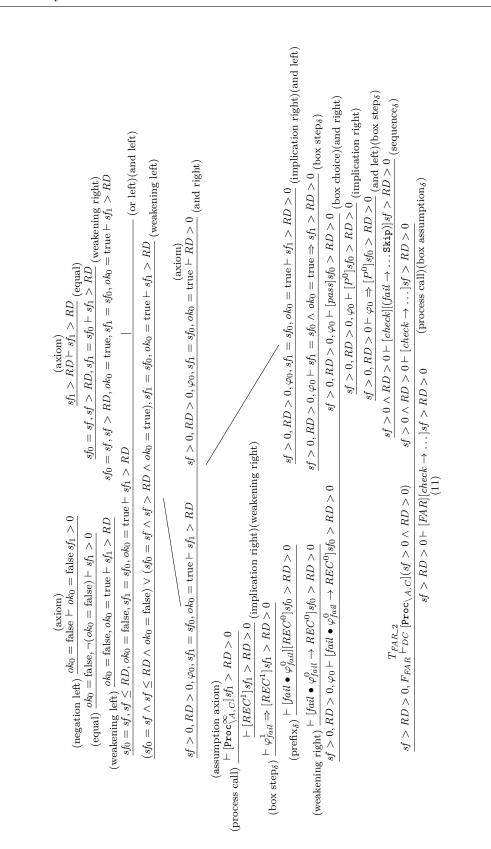

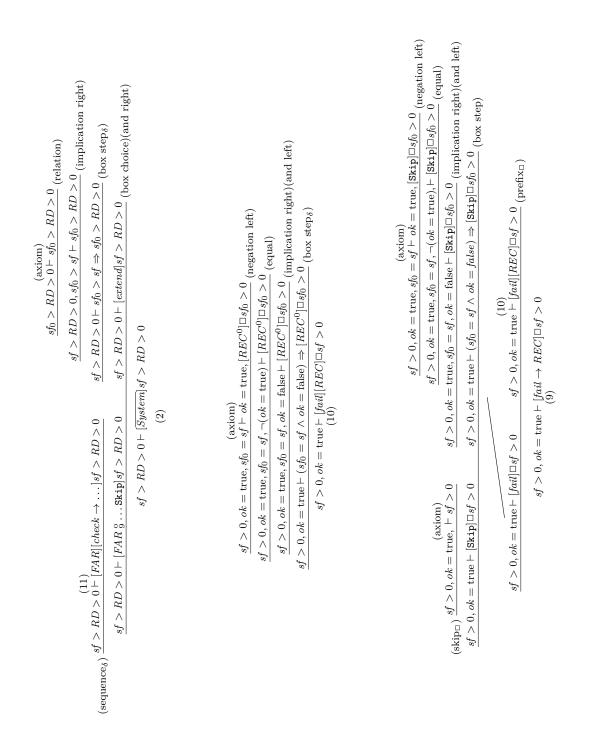

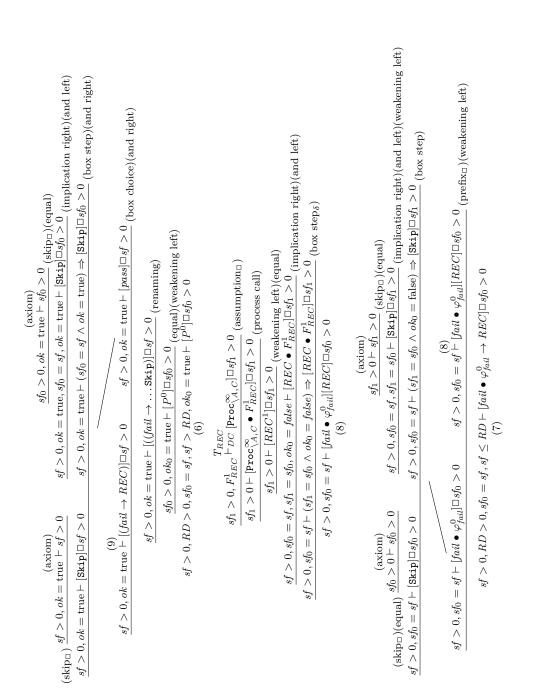

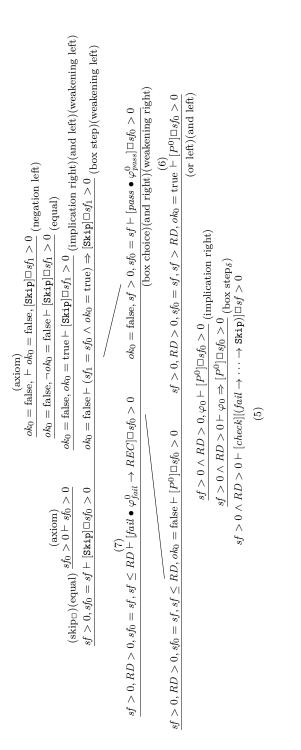

|    |      | A.1.1. Proof Tree for the VA                                                               |     |

|    |      | A.1.2. CSP-OZ-DC Model of the Train Control System                                         |     |

|    |      | A.1.3. CSP-OZ-DC Representation of the VA                                                  | 243 |

|    |      | A.1.4. Alternative Architecture without eCSP $\ldots \ldots \ldots \ldots$                 |     |

|    | A.2. | ETCS Emergency Message Case Study                                                          | 247 |

| A.2.1. Original CSP-OZ-DC    | Specification from [MFHR08] | 247 |

|------------------------------|-----------------------------|-----|

| A.2.2. VA Proof Tree for the | e ETCS Case Study           | 250 |

| A.2.3. Modified CSP-OZ-DO    | C Specification Matching VA | 257 |

| Bibliography                 |                             | 263 |

| Sequent Rules                |                             | 279 |

| Glossary of Symbols          |                             | 281 |

| Index                        |                             | 287 |

## List of Figures

| 1.1. Context of this thesis31.2. Scenario of running example51.3. Illustration of a Verification Architecture7 |  |

|----------------------------------------------------------------------------------------------------------------|--|

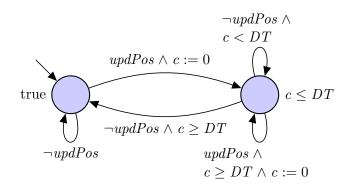

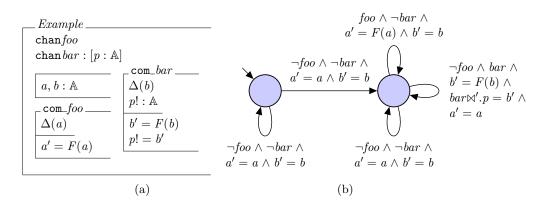

| 2.1. Exemplary CSP-OZ-DC specification                                                                         |  |

| 2.2. Exemplary Phase Event Automaton                                                                           |  |

| 2.3. A PEA representing a process of Fig. 2.1                                                                  |  |

| 2.4. Translation of the OZ part into PEA                                                                       |  |

| 4.1. Proof tree for Example $4.3.2$                                                                            |  |

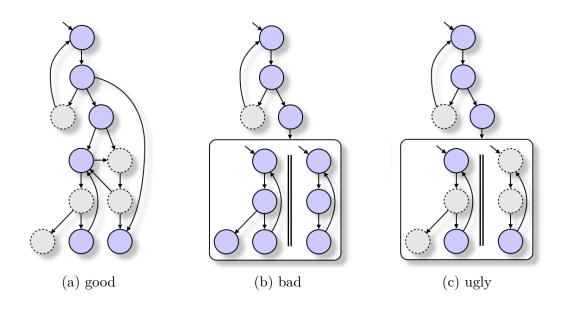

| 4.2. Protocol structures to be handled with the DL approach 99                                                 |  |

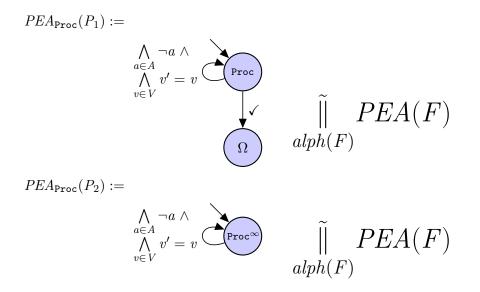

| 6.1. Translation of unknown processes into PEA                                                                 |  |

| 6.2. Sequent-style proof rules for timing properties                                                           |  |

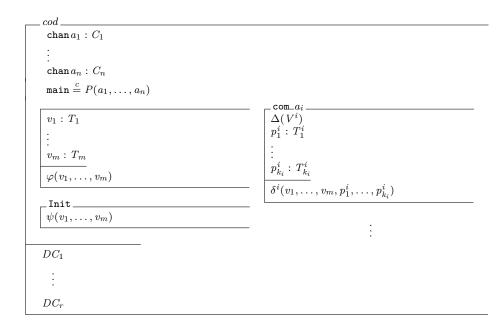

| 6.3. Generic CSP-OZ-DC specification <i>cod</i>                                                                |  |

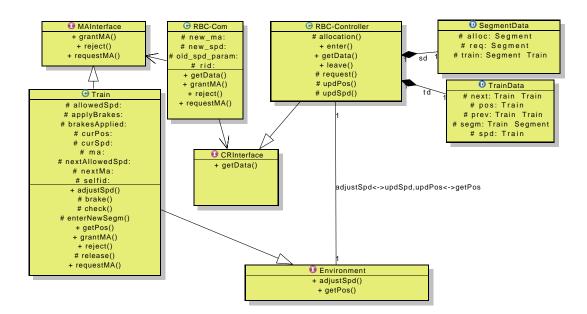

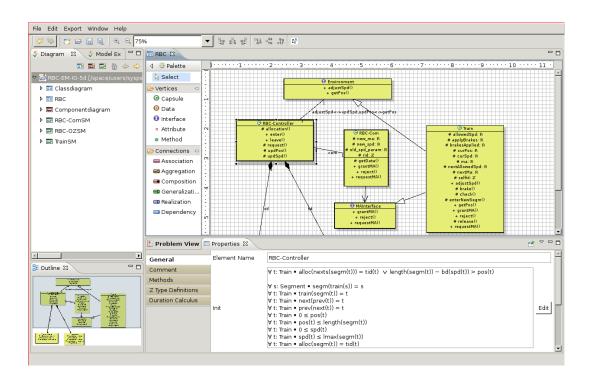

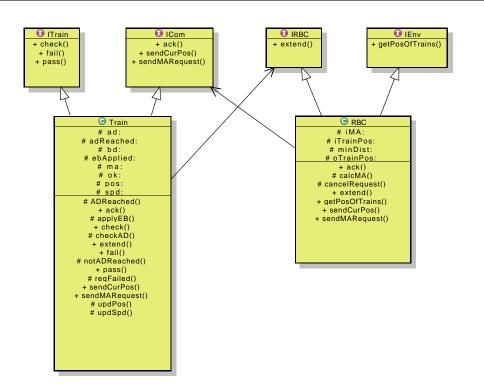

| 7.1. An exemplary class diagram                                                                                |  |

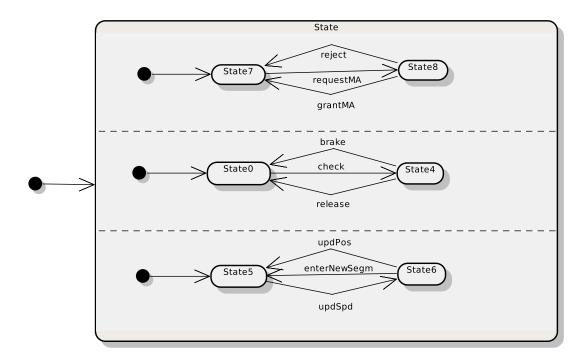

| 7.2. State machine for Train                                                                                   |  |

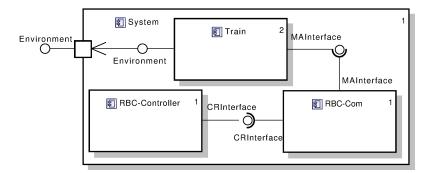

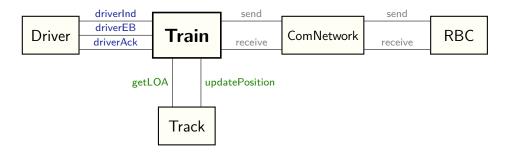

| 7.3. Exemplary component diagram                                                                               |  |

| 7.4. Screenshot of Syspect                                                                                     |  |

| 7.5. Syspect verification toolchain                                                                            |  |

| 7.6. Counterexample view in Syspect                                                                            |  |

| 7.7. VA of the running example modelled in Syspect                                                             |  |

| 7.8. Tool chain for VA plug-in                                                                                 |  |

| 8.1. Scenario of the small train control example                                                               |  |

| 8.2. VA for the train control system                                                                           |  |

| 8.3. Syspect class diagram for the train control system                                                        |  |

| 8.4. Part of the train specification                                                                           |  |

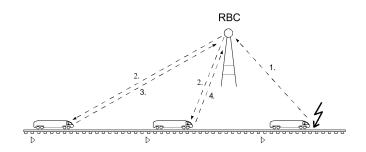

| 8.5. Case study scenario                                                                                       |  |

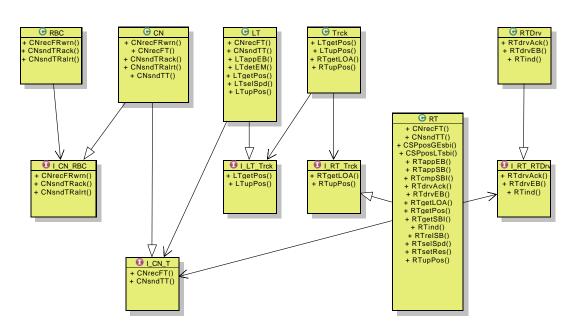

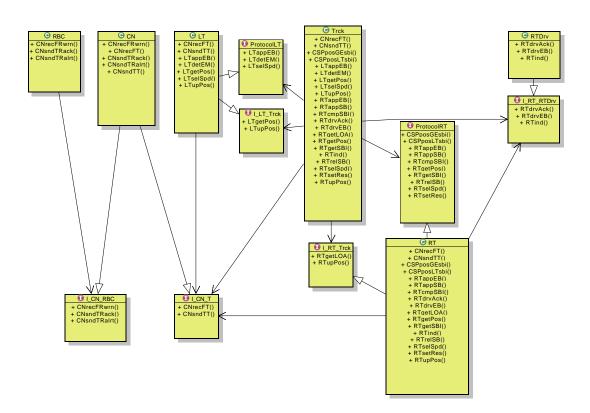

| 8.6. Components of the Case Study                                                                              |  |

| 8.7. Signature for the ETCS VA                                                                                 |  |

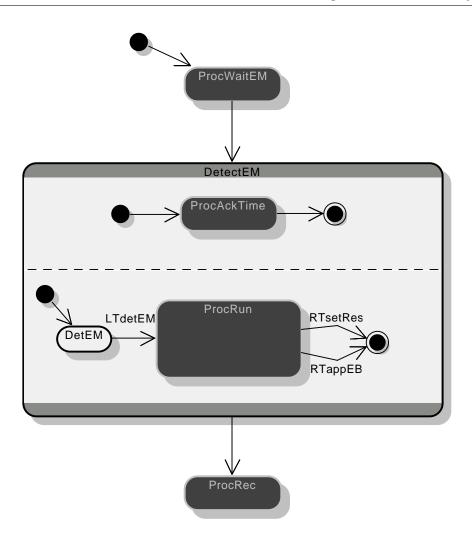

| 8.8. The VA process ETCS-EM for the ETCS case study                                                            |  |

| 8.9. The VA process as modelled in Syspect                                                                     |  |

| 8.10. DC assumptions on the protocol phases                                                                    |  |

| 8.11. Representation of the parallel composition without unknown parts $~$ 210                                 |  |

| 8.12. Representation of $\mathit{ProcFree}$ without constraints over clocks |   |  | • | 210 |

|-----------------------------------------------------------------------------|---|--|---|-----|

| 8.13. Proof tree for timing constraints                                     |   |  |   | 212 |

| 8.14. Side-conditions to be checked for $(T1)$ up to $(T3)$ of page 212     |   |  |   | 213 |

| 8.15. Syspect class diagram for the ETCS case study                         |   |  |   | 214 |

| 8.16. Control structure of class $Trck$ as modelled in Syspect              |   |  |   | 215 |

| 8.17. Class diagram with <i>Trck</i> as protocol class                      |   |  |   | 216 |

| 8.18. Process representing the control structure of the ETCS model          | • |  |   | 217 |

# 1 Introduction

People want to forget the impossible. It makes their world safer.

(Silas, in The Graveyard book, Neil Gaiman)

| 1.1. | Running Example: A Small Train Control System                | 5  |

|------|--------------------------------------------------------------|----|

| 1.2. | Overview of the VA Approach                                  | 6  |

| 1.3. | Related Work on Pattern-Based and Compositional Verification | 8  |

| 1.4. | Structure of this Thesis                                     | 11 |

| 1.5. | Acknowledgements                                             | 12 |

Systematic analysis of software and hardware is an important instrument to increase the safety of computer systems, and this is particularly relevant when designing systems in safety critical application domains like transportation systems or industrial plants whose malfunction may endanger monetary investments, environment, or life. For this reason, there is a lot of ongoing research with the aim of helping system engineers to develop high-quality software or hardware that is guaranteed to answer the desired purpose. There are two major research directions to tackle these issues.

On the one hand, *informal software engineering approaches* aim at methods and tools to capture the complexity of a system which usually can only be handled based on the division of labour. Systematic and standardised techniques are investigated, like development processes, architectural concepts, modelling languages, and quality control. The main focus of those techniques is to increase the quality of complex software systems during the entire development and life cycle.

On the other hand, *formal analysis techniques* are also targeted to increase the quality of software systems, but these techniques approach from the side of rigor-

#### 1. Introduction

ously mathematical methods. Systems are described by languages that are often not focused to convenient applicability when developing large software systems, rather having a well-defined semantics in a mathematical domain that can be exactly analysed. Ideally, those analyses are performed completely automatic with the help of sophisticated verification tools. To cope with the increasing complexity of software systems, abstraction techniques and decompositional methods are applied for reducing the state space, particularly for infinite state systems, and for partitioning verification problems into smaller parts.

In this thesis, we integrate techniques of both worlds that have been proven to be successful in their application domain, in order to bundle the advantages of the approaches and to overcome specific difficulties from which both suffer.

**Informal analysis of complex real-time systems.** The subject of this work are basically complex, safety-critical systems, i.e., systems for which specific safety properties are indispensable. This includes plenty of daily-life software systems: for instance, automated cruise-control systems or safety systems of modern vehicles, medical equipment, power plants; wherever technical systems take over control from humans. Suchlike systems are often inherently complex, because they are determined by orthogonal system dimensions. When analysing this complexity, it turns out that there is hardly a single formalism that adequately describes all relevant aspects. Hence, in practice system engineers often fall back on combinations of different techniques for system analysis. To cope with heterogenous system dimensions, the Unified Modelling Language (UML) [RJB99, Dou97, Dou04] has been developed, combining multiple graphical notations for different views of a design. But even though UML meets the identified requirement to comprehensively capture the system dimensions of complex systems by providing diagrammatic modelling techniques and even though it is well-integrated into industrial software development processes, it lacks an important feature that is necessary for the integration into *formal* software analysis: an exact semantics. In practice, this leads to misconceptions and misunderstandings in software development, and UML cannot directly be used in combination with formal verification techniques.

A further concept to reduce the complexity of software designs is the use of *design* patterns [GHJV95, SSRB00, Dou02], which allow developers to structure large design problems into smaller parts for which standardised solutions exist. Once a solution to a dedicated design problem is realised with patterns, they can be reused in different contexts. However, similarly to UML, pattern-based approaches are usually applied informally, often described by textual, tabular, or graphical representations. Thus, suchlike pattern-based techniques are generally incompatible with formal analysis.

**Formal analysis of complex real-time systems.** In the world of formal analysis and verification there has been a lot of work on integrating specification techniques to condense advantages of single formalisms into combined formalisms, e.g., [But92,

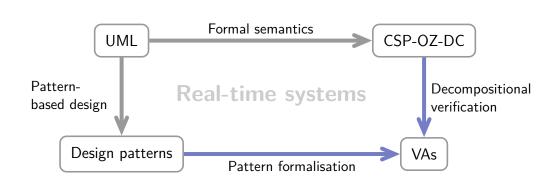

Figure 1.1.: Context of this thesis

RAI92, MD98, AM98, Fis00, WC01, Süh02, SLD08]. In the analysis of safety-critical real-time systems, several important aspects have to be covered by a formalism in order to cope with the complexity of the system:

- 1. behaviour that conforms to communication protocols and the internal control flow of components,

- 2. rich data structures with possibly infinite domains, e.g., linked lists or real numbers, and

- 3. timing constraints such that the system reacts timely to external events.

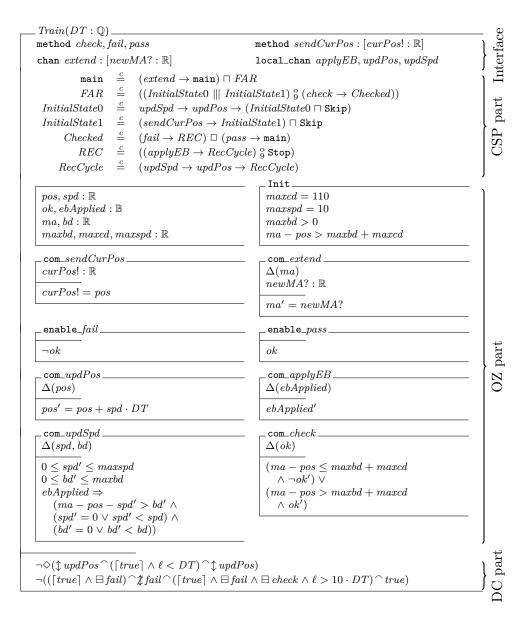

An example for such a combined specification formalism is *CSP-OZ-DC*, which was developed by Hoenicke and Olderog [HO02a, HO02b, Hoe06]. CSP-OZ-DC integrates the well-investigated formalisms *Communicating Sequential Processes (CSP)*, to specify the control flow, *Object-Z (OZ)*, to define the data space and data changes, and *Duration Calculus (DC)*, to impose dense real-time constraints on system specifications. In [Hoe06, MFHR08] an operational semantics and a model checking approach for CSP-OZ-DC are presented, such that CSP-OZ-DC can be used for formal analysis of real-time systems with automated methods. Furthermore, in [MORW08, FLOQ11] CSP-OZ-DC is integrated into the software engineering process with UML by providing a UML profile for real-time systems. This profile defines a subset of UML diagrams, in which the elements hold certain additional annotations; a translation of this profile into a CSP-OZ-DC semantics is given. By this means, real-time systems can be specified with UML and formally analysed and verified with CSP-OZ-DC.

However, a major problem remains: suchlike integrated formal techniques, for which CSP-OZ-DC is an example, are designed for heterogeneous and thus inherently complex systems, and when formally verifying those systems, we have to cope with this complexity. Even though integrated specifications can often be translated into leaner formalisms, these still need to cover all relevant information. Particularly, systems with a large degree of concurrency often suffer from the state space explosion problem. Thus, formal analysis of those systems is only applicable if they are decomposed in a suited manner into smaller parts.

Idea of the Verification Architecture approach. To solve the identified complexity issues for heterogenous real-time systems, we carry the ideas of informal design patterns over to formal specifications. To this end, a formalisation of patterns for complex real-time systems, so-called *Verification Architectures (VA)*, is introduced. Moreover, we examine how these VAs are verified with respect to desired safety properties, and how they enable compositional verification of complex systems specified with combined specification languages. Figure 1.1 gives an overview of the context of this work and the interrelation of informal models (represented by 'UML' in the diagram) and design patterns in contrast to formal specifications (represented by 'CSP-OZ-DC') and Verification Architectures.

The benefits of the Verification Architecture approach are twofold: First, analogous to design patterns, VAs can be reused in different applications. In doing so, verified properties of the VA are inherited by all instances. Second, VAs give rise to a decomposition of the system: global properties are verified by combining local analyses. This idea originates from previous case studies [MFHR08] in the context of the transregional research centre AVACS<sup>1</sup>, where a specification of the European Train Control System (ETCS) [ERT02] was decomposed according to its abstract behavioural protocol. The protocol splits the system runs into several phases (e.g., braking phase and running phase) with local real-time properties that hold during these phases. After showing the correctness of a desired global property for the protocol, this property is also guaranteed by all instances of the protocol that satisfy the local properties. Since the local properties correspond only to parts of the protocol, it is more efficient to verify the local properties instead of directly checking the global safety property. In case of the ETCS case study, the latter was not possible due to the size of the case study model, while verification of the local properties was successful [MFHR08]. We generalise and formalise this approach in the context of combined languages. The approach is structured into several layers:

- 1. abstract behavioural *protocols with unknown parts*, which have a large degree of freedom to comprise a large class of concrete systems, need to be specified and verified with respect to desired *global safety properties*;

- 2. since the analysed systems are often time-dependent, it is important to allow imposing of additional *local real-time assumptions* on protocol phases, and it must be possible to verify the protocols taking these assumptions into account;

- 3. it needs to be checked that concrete systems, given as combined specifications to capture heterogeneous systems, are *instances* of the protocol;

- 4. it needs to be checked that concrete instances actually guarantee the local realtime assumptions on the protocol phases.

The challenge is to tackle each layer of the problem with a suitable formalisation and to integrate the heterogeneous formalisations into a uniform framework.

<sup>&</sup>lt;sup>1</sup>http://www.avacs.org

**Summary of contributions.** We introduce a pattern-based Verification Architecture approach for complex (dense) real-time systems, a new conceptional approach on how to use behavioural protocols as a decomposition technique to enable verification of systems specified by combined formalisms. By establishing behavioural design patterns for suchlike formalisms, we extend existing work on integrating combined formalisms and software engineering processes. In particular, when using VAs in combination with CSP-OZ-DC, we benefit from its descriptive UML representation and graphical tool support.

Beyond this conceptional contribution, we present a theoretical model based on CSP for the specification of VAs. The verification approach for VAs makes use of theorem proving as well as model checking: an embedding into Dynamic Logic and a sequent-style proof calculus for the VA model are introduced, whereas local assumptions are verified with existing model checking techniques. A refinement notion for VAs is established that is used to automatically prove that a concrete model instantiates a VA, by which the model inherits all safety properties of the VA. Finally, we demonstrate our approach using a case study from the AVACS sub-project R1.

In the following, the basic technical details of the VA approach are introduced. But beforehand, we present a running example that is used throughout this thesis.

#### 1.1. Running Example: A Small Train Control System

The emerging European Train Control System (ETCS) is an international standard [ECS99, ERT02] that shall replace national train control systems to ensure crossborder interoperability and to improve railway safety as well as track utilisation. In the final ETCS implementation level, the existing national trackside systems for detection of train speed, location, and integrity will not be used anymore. Instead, a radio block centre (RBC) controls the traffic in a well-defined area. It ascertains speed and position values in cooperation with the ETCS on-board units of the trains. RBCs and trains communicate over a GSM-R radio connection. One objective of the ETCS is to increase the possible

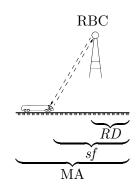

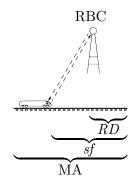

Figure 1.2.: Example

traffic density. For this purpose, the *moving block principle* is used, by which a *movement authority* is always granted up to a position closely behind the preceding train. In case of an accident, the train control system has to stop all trains safely.

The setting is pictured in Fig. 1.2: an RBC grants movement authorities (MAs) to a train. The system is considered safe as long as the train stays within the MA. The distance of the train to the end of the MA is given by a real-valued variable sf, reflecting the safety of the system, that shall never be below 0. The *reaching distance* position RD is the last position at which the train needs to apply the brakes to stop

in time. To ensure safety, the system shall comply with a simple protocol structuring all runs into phases: The first protocol phase FAR describes the situation where the train is in a safe mode with a large distance to the end of the MA. In a second phase CHK, the train is required to check the distance to the end of the authority and to take an appropriate action: either it may request an extension of the MA (REQ) or—if the train is too close to the end of the MA—it changes to a recovery phase REC in which a counteraction is initiated, e.g., application of emergency brakes in order to stop the train safely.

This is a typical protocol that can be realised as a VA: it comprises some defined behaviour (for instance, the decision which is necessary when the train is too close to the end of the MA), real-time constraints (the train has to check the situation within certain time intervals), and some unknown behaviour that is not relevant for the protocol (it does not matter how the train behaves in the FAR phase as long as the train is not too close to the end of the MA).

This example is to be continued during this thesis and we will show how such protocols are specified, verified, and instantiated.

#### 1.2. Overview of the VA Approach

We now introduce the ideas and basic formalisations of our approach to use patterns for the compositional verification of real-time systems.

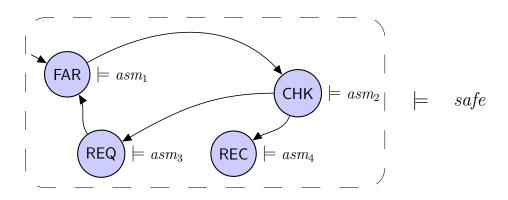

**Generic protocol.** A Verification Architecture (VA) is a formalisation of a generic protocol with local real-time assumptions that ensures the safety of a class of systems. We use parametric *CSP processes with data constraints and unknown parts* to specify VAs. A VA consists of a parametric CSP process, enriched by data constraints, and additionally, of assumptions on specific phases of the generic protocol, defined as formulae in an arbitrary real-time logic. In our examples, we will use Duration Calculus (DC) to specify local assumptions. Figure 1.3 depicts a VA in the dashed box. The locations represent phases of a protocol (for instance, the protocol phases *FAR*, *CHK*, *REQ* and *REC* of the running example) with additional local assumptions  $asm_1$  up to  $asm_4$ .

The name *Verification Architecture* reflects the purpose of the protocol, which is dedicated to formal verification by decomposing a global property into local properties of protocol phases. We use the terms *Verification Architecture* and *protocol* (that is formalised as VA) synonymously. If we refer only to the structure of the protocol process without the local assumptions, we use the notion *protocol structure*.

**Proof rules.** We use a rule-based sequent calculus to establish the validity of global properties (e.g. *collision freedom* for the running example in Sect. 1.1) for VAs. To this end, we have to take into account the timed assumption on the protocol phases as well as the data constraints.

Figure 1.3.: Illustration of a Verification Architecture

**Concrete instantiations.** We consider concrete instances of systems that conform to VAs. We show when such instances actually refine the process structure of the corresponding VA. To this end, we present a proof rule that allows us to check syntactically that the structure of a concrete CSP-OZ-DC specification conforms to a VA.

**Correctness of local assumptions.** One has to prove that every process of a concrete instance that refines a protocol phase of the VA satisfies every corresponding local assumption of the phase. For instance, a process instantiating the FAR phase of the example is required to satisfy  $asm_1$ , which is a property stating that the train is not moving too fast. This step is done with a suited verification technique for the logic of the assumptions. For example, in the case of DC and CSP-OZ-DC the verification approach of [MFHR08] is used. The local assumptions only depend on parts of the CSP-OZ-DC model and, thus, the resulting verification tasks are simpler than the global safety property.

**Guaranteed correctness.** Finally, if the structural refinement relation and the local assumptions are valid, our VA approach guarantees that the global safety property is also valid for the entire model.

#### Formalisation of the VA Approach

We give a formalisation of the problem. Let  $prtcl(\overline{p}, P_1, \ldots, P_n)$  be an abstract behavioural protocol depending on a vector of data parameters  $\overline{p}$  and on process parameters  $P_i$ . Additionally, we consider temporal assumptions  $asm_1(\overline{p}), \ldots, asm_n(\overline{p})$  on the  $P_i$ , which may also depend on the data parameters  $\overline{p}$ . We denote the combination of protocol structure and temporal assumptions as *Verification Architecture* (VA). Our aim is to show that a safety property  $safe(\overline{p})$  is valid for every possible model which is a refinement of the behavioural protocol and which respects the assumptions. To apply our approach, we have to show that the VA is correct, i.e., the protocol is correct for all parameters and processes respecting the assumptions:

$$\forall \,\overline{p}, P_i \bullet \left( \bigwedge_{i=1,\dots,n} P_i \models asm_i(\overline{p}) \right) \Rightarrow (prtcl(\overline{p}, P_1, \dots, P_n) \models safe(\overline{p}))$$

(1.1)

We will provide proof rules for the verification of this proof task. Once it is verified, this result is reusable as all instances of this architecture inherit the correctness property automatically. We only have to show that it is a refinement of the protocol structure and that the local assumptions are valid, which is due to their locality easier than to verify the global property directly. We consider an instance  $spec(\bar{p}, P_1^0, \ldots, P_n^0)$  of the abstract protocol, where the  $P_i^0$  are instances of the process parameters. First, we have to show that every trace of the instance is also a trace of the protocol:

$$\forall \,\overline{p} \bullet [\![spec(\overline{p}, P_1^0, \dots, P_n^0)]\!] \subseteq [\![prtcl(\overline{p}, P_1^0, \dots, P_n^0)]\!].$$

(1.2)

This relation is shown syntactically for a specific class of instances (cf. Sect. 5.1). Second, we have to show that the assumptions are valid for the concrete specification:

$$\forall \,\overline{p} \bullet P_i^0 \models asm_i(\overline{p}) \text{ for all } i \in 1..n.$$

(1.3)

This is done by applying existing verification techniques for the language of the assumptions. With this, our approach yields that the desired safety property is valid for the concrete model. We argue that this proposition is correct. From (1.1) and (1.3) we can conclude (1.4), and with (1.2) we get the desired property (1.5).

$$\forall \,\overline{p} \bullet prtcl(\overline{p}, P_1^0, \dots, P_n^0) \models safe(\overline{p})$$

(1.4)

$$\forall \,\overline{p} \bullet spec(\overline{p}, P_1^0, \dots, P_n^0) \models safe(\overline{p}) \tag{1.5}$$

We summarise that if a correct VA is given, we only have to show that (1) a concrete model is actually a structural refinement of the abstract protocol, and (2) the model respects the local assumptions. Then we can conclude the correctness of the entire model.

#### 1.3. Related Work on Pattern-Based and Compositional Verification

We present a formal and generic framework for reusable verification patterns that are used to decompose a specification and to simplify verification of complex systems. To this end, the VA approach involves formal analysis on several stages:

1. behavioural protocols (comprising data aspects and allowing for a large degree of freedom) with a formal semantics

- 2. verification of these protocols (proof calculus)

- 3. refinement by concrete specifications

- 4. combination with higher-level specifications (e.g., CSP-OZ-DC and the UML profile for CSP-OZ-DC)

- 5. formal verification of local assumptions (e.g., by model checking)

- 6. inheritance of safety properties

Other works on formal design patterns often focus on single aspects or on handling of standard design patterns (considering static analysis of code and structures in object-oriented languages) in contrast to the behavioural, protocol-based pattern we consider here. In the following, we review related pattern-based and decompositional approaches.

**Design Patterns.** Our approach is inspired by [DHO06], where for a fixed DC protocol, a design pattern for cooperating traffic agents is introduced. The work [KRS07] presents Design Verification Patterns, which are also motivated by [DHO06]. These patterns are introduced as a formal counterpart to the well-known design patterns from classical software engineering. [KRS07] proposes to use Rely-Guarantee pairs as proof obligations to characterise patterns and exemplary gives such pairs for two design patterns. But contrary to the Verification Architectures approach, no formal framework for the use and application of design patterns is introduced. It is neither examined how to verify the patterns itself nor exploited that the pattern may lead to a natural decomposition for verification. Moreover, no tool support for automated verification is provided.

A general overview on formalisation techniques for design patterns is contained in [Tai07], but without considering verification of real-time systems. Instead, several formalisation approaches and languages are listed, basically with the aim to avoid the ambiguity of standard design patterns. An example is [FCA07], where object-oriented design patterns, like the Observer pattern [GHJV95], are specified in terms of the RAISE Specification Language [RAI92]. Other works with a similar focus to design patterns for static organisation of specifications, can be found in [SH04, BH07]. On the contrary, we consider behavioural protocol patterns used for formal verification of real-time systems. The work [HKM07] is more related to our approach: they also consider behavioural design patterns, which are specified in the experimental Ocsid language and verified by theorem proving. The desired properties are specified with linear-time temporal logic. The patterns are used for synthesis of instances, whereas we use a syntactic refinement check to establish a connection between pattern and instance. Additionally, they do not examine real-time specifications and do not present a formal framework for the decompositional verification of complex systems using design patterns.

Pattern-based approaches for real-time systems, e.g., [TZY<sup>+</sup>03, DHQ<sup>+</sup>04, KC05, FVVC06], often introduce timing patterns for bounded response, task periods, etc., contrary to our work, where arbitrary real-time properties are imposed on protocols.

A behavioural design pattern method that is similar to ours is realised in the context of the Fujaba tool suite [GTBF03, Gie03]: design patterns are specified with discrete-time state charts without data and syntactically instantiated by refinement. This work is reviewed in more detail in Sect. 7.4.

**Compositional methods.** To establish global properties of a VA, their correctness has to be shown under certain local assumptions over unknown components. When verifying that a concrete specification is an instance of the VA, these assumptions have to be checked such that the instance is guaranteed to inherit the desired global property. By this means, the VA approach is similar to classical Assume-Guarantee (A-G) reasoning (in the context of combined, parametric specifications), where properties over components are shown under the assumption that the environment satisfies specific 'Assume' properties. A-G reasoning was initially introduced in the early 80s in [MC81, Jon81] and has been developed further in several works, e.g., [AL93, AL95, FMS98, MCF<sup>+</sup>97]. The work [dRdBH<sup>+</sup>01] contains a general introduction into A-G reasoning without time and without the context of conjoint verification techniques.

In contrast to our approach, classical A-G approaches usually consider components together with assumptions on the environment of a component, i.e., components are analysed with respect to a parallel environment. In the VA approach, assumptions over unknown protocol parts are integrated into more complex protocol structures, also incorporating sequential and parallel composition as well as recursion. However, existing A-G methods can be used to complement our approach to solve properties over parallel unknown components. In particular, we apply *Rely-Guarantee* reasoning in Sect. 6.1.3, which is a sub-form of A-G reasoning dedicated to shared variable systems; we adapt Rely-Guarantee reasoning for the handling of properties of parallel unknown components. In a similar way, it will be possible to adapt other existing A-G methods to the VA approach.

In [MWW08, Met10] an A-G verification approach for CSP-OZ (without time) is presented that does not consider decompositions by given protocols but instead uses a learning-based algorithm to generate assumptions on layered components.

An approach with basic ideas similar to ours was developed by D'Errico and Loreti [DL09, DL10]: they investigate concrete CCS processes [Mil80] with an unknown environment that is constrained by Hennessy-Milner logic [HM85]. They provide a compositional proof system based on A-G reasoning for these processes and introduce a notion of property-preserving refinements of the unknown parts. The main difference to the work presented here is that they are focused on simple, only event-based, CCS processes and Hennessy-Milner logic and consider no more complex or combined specification languages and neither real-time properties nor data constraints.

#### 1.4. Structure of this Thesis

In this first chapter, we have motivated the usage of the conceptual Verification Architecture approach in the context of informal and formal models of software systems. We have introduced the basic idea of VAs to use abstract behavioural protocols to structure verification tasks. By this means, VAs are used as a decomposition technique to enable verification of complex systems specified by combined formalisms.

- In Chap. 2, we preliminary present basic formalisms that are needed throughout this work. These are the combined formalism CSP-OZ-DC and Phase Event Automata, a timed automata model for the operational semantics of CSP-OZ-DC.

- Chapter 3 introduces a new CSP dialect *eCSP* that extends classical CSP by data constraints and unknown processes with local real-time assumptions for the specification of VAs. Furthermore, we analyse semantical properties of this CSP dialect and present two useful normal forms.

- To prove properties over eCSP, it is embedded into Dynamic Logic in Chap. 4. A sequent calculus for this logic is introduced and proven correct.

- In Chap. 5, we establish a notion of refinement for eCSP and for combined specifications in terms of CSP-OZ-DC. Moreover, we present efficient, syntactical rules to prove that a CSP-OZ-DC specification is a structural refinement of an eCSP process, and we analyse property inheritance for the refinement relation.

- Limitations and possible extensions of the VA approach are discussed in Chap. 6. In particular, we examine how parallelism over unknown parts is solved and present a second semantics for eCSP that is suited to adequately describe parallelism over unknowns. We compare the different semantics of eCSP and discuss shared variable access in eCSP. In addition, we shortly analyse verification of timed properties and completeness issues. An examination of decomposition techniques that complement the VA approach concludes the chapter.

- Chapter 7 shows how the VA approach is embedded into a software engineering process: a graphical UML tool is presented that supports Verification Architectures and the UML profile for CSP-OZ-DC.

- The application of the VA approach is demonstrated in Chap. 8 by two case studies: the train control system of the running example and a larger ETCS case study from the AVACS sub-project R1.

- Finally, Chap. 9 concludes this thesis with a general discussion and an evaluation of the VA approach.

• In the appendix, the reader finds a glossary of symbols and an index, which might be helpful while reading this thesis. Furthermore, a list of all rules of the introduced sequence calculus and auxiliary case study material are provided.

#### Sources

Some parts of this thesis are based on previously published works by the author (most of them significantly revised):

- Section 1.2 is partly taken from [Fab10a].

- Parts of Chap. 2 contain adapted material from [FS07] (Sect. 2.1.1), [FJSS07, MFHR08] (Sect. 2.3), and from [FLOQ11] (the part about the CSP-OZ-DC translation into PEA).

- Chapter. 3 is based on [Fab10b, Fab10a].

- Parts of Chap. 7 (Sect. 7.1 and 7.2) are taken from [FLOQ11], which is joint work with Sven Linker, Ernst-Rüdiger Olderog, and Jan-David Quesel.

- The running example (Sect. 8.1, App. A.1) was presented in [Fab09, Fab10b].

- The ETCS case study in Sect. 8.2 and the CSP-OZ-DC model in App. A.2.1 are based on case study material in [MFR06, FM06, MFHR08], which is joint work with Roland Meyer, Jochen Hoenicke, and Andrey Rybalchenko, but the VA and the modified ETCS model are presented here for the first time.

#### **1.5.** Acknowledgements

This thesis would not have come to fruition without many people who contributed in one or another way to this work: current and former colleagues of the working group *Correct System Design*, who provided me with a very friendly working atmosphere, useful hints and encouragement; the students who implemented important parts of Syspect, the PEA toolkit, and Moby/PEA; colleagues from AVACS and Paderborn with whom I discussed my research and who developed the verification approaches used in this work and the tools ARMC and SLAB; and my friends and my family, who were listening to me for several years whenever I got stuck with my work.

I am deeply grateful to all of you!

I want to express my particular gratitude to Ernst-Rüdiger Olderog for giving me the opportunity and the necessary freedom to develop my research ideas and for always having an open office for me. I thank Bernd Finkbeiner for agreeing to act as a co-referee even in face of the coincidence with the AVACS review process.

Furthermore, I sincerely thank Melanie Faber, Henrik Lipskoch, Christian Schultz-Brummer, Esther and Caleb McDonald, and Jörn Störk for proofreading parts of this thesis.

# 2 Preliminaries

You know something? We came here for you, a long time ago, when you died. Well, it wasn't here and that wasn't you, but we did anyway.

(Delirium, in The Wake, Neil Gaiman)

| 2.1. CSP, OZ, and DC                                           | 14 |

|----------------------------------------------------------------|----|

| 2.1.1. Communicating Sequential Processes                      | 14 |

| 2.1.2. Object-Z                                                | 17 |

| 2.1.3. Duration Calculus                                       | 22 |

| 2.2. Combining CSP, OZ, and DC Into a Parametric Specification |    |

| Language                                                       | 26 |

| 2.2.1. Syntax of CSP-OZ-DC                                     | 28 |

| 2.2.2. Semantics of CSP-OZ-DC                                  | 30 |

| 2.2.3. Related Combined Approaches                             | 32 |

| 2.3. Phase Event Automata                                      | 33 |

| 2.3.1. Syntax and Semantics of Phase Event Automata            | 33 |

| 2.3.2. Operational CSP-OZ-DC Semantics in Terms of PEA $\ .$   | 38 |

The focus of this thesis is on the analysis and verification of complex real-time systems that are determined by heterogeneous system dimensions. To cope with such different dimensions, Hoenicke and Olderog introduced CSP-OZ-DC [HO02a, HO02b] that combines three well-investigated formalisms into a single language: it uses CSP [Hoa85, Ros98] to model the control flow of a system, Object-Z (OZ) [Smi92, Smi00] to specify data space and state changes via OZ schemata, and it applies a restricted class of DC formulae [ZHR91, ZH04] for defining (dense) real-time constraints. CSP-OZ-DC is a declarative and object-oriented language. A key feature of CSP-OZ-DC is its separation of concerns, because every part, i.e., the control flow, the data space, and the timing part can be specified on its own. Its semantic is given in terms of interpretations, and it is compositional. Thus, if one can establish a safety property for a single part of the specification the property automatically holds likewise for the entire specification.

Due to this features, we make use of CSP-OZ-DC in the context of Verification Architectures, particularly, as specification language for concrete instances of architectures and for our case studies in Chap. 8. In this chapter, we introduce CSP-OZ-DC and a model for its operational semantics in detail.

#### 2.1. CSP, OZ, and DC

#### 2.1.1. Communicating Sequential Processes

Communicating Sequential Processes (CSP) is a notation to describe concurrent and sequential processes. It was initially developed by C.A.R. Hoare [Hoa78, Hoa85]. Its basic building units are instantaneous events that can be arranged into processes using process algebraic operators, e.g., for sequential or parallel composition. We denote the set of all events by *Events* and the set of events occurring in a process P, the alphabet of P, by alph(P).

#### Syntax of CSP

The CSP syntax is defined by the following BNF grammar:

$$\begin{split} P &::= \operatorname{Stop} \mid \operatorname{Skip} \mid a \to P \mid P_1 \Box P_2 \mid P_1 \sqcap P_2 \mid \\ P_1 \parallel_A P_2 \mid P_1 \parallel P_2 \mid P_1 \stackrel{\circ}{_{9}} P_2 \mid P[R] \mid P \setminus A \mid X. \end{split}$$

We denote the so-defined set of process expressions with *Process*, *Process* == *P*. The process **Stop** denotes a deadlocking process, **Skip** a terminating process. For an event  $a \in Events$ ,  $a \to P$  denotes a process that communicates the event *a* and then behaves as the process *P*. The operators  $\Box$  and  $\Box$  represent external choice and internal choice, respectively. An external choice is resolved by the environment of the process, while internal choice is non-deterministically resolved by the process itself. Concurrent processes are described by  $||_A$  and |||. The former operator is used for processes that synchronise on events from a set  $A \subseteq Events$ , and the latter for interleaved processes, i.e., the process behaves like  $P_1$  until the process terminates and then it behaves like  $P_2$ . Hiding of events from a process can be specified with  $\backslash$ . The operator P[R] renames the events in *P* according to a relation *R* on events. Finally, *X* stands for a process identifier, which must be declared with an expression

$X \stackrel{c}{=} P$  and which can be used to recursively define processes. Another representation of recursive processes is the fixed point expression  $\mu X \bullet F(X)$ .

**Example 2.1.1.** As example we consider the following CSP process equation system specifying a train component for the running example of Sect. 1.1.

| main                  | $\stackrel{c}{=}$ | $(extend \rightarrow \texttt{main}) \sqcap FAR$                                    |

|-----------------------|-------------------|------------------------------------------------------------------------------------|

| FAR                   | <u></u>           | $((InitialState0 \parallel   InitialState1) \ _{9} \ (check \rightarrow Checked))$ |

| ${\it InitialState0}$ | $\stackrel{c}{=}$ | $updSpd \rightarrow updPos \rightarrow (InitialState0 \sqcap \texttt{Skip})$       |

| InitialState1         | $\stackrel{c}{=}$ | $(sendCurPos \rightarrow InitialState1) \sqcap \texttt{Skip}$                      |

| Checked               | $\stackrel{c}{=}$ | $(fail \rightarrow REC) \ \square \ (pass \rightarrow \texttt{main})$              |

| REC                   | $\stackrel{c}{=}$ | $((\textit{applyEB}  ightarrow \textit{RecCycle}) \ _{9}^{\circ} \ \texttt{Stop})$ |

| RecCycle              | $\stackrel{c}{=}$ | $(updSpd \rightarrow updPos \rightarrow RecCycle)$                                 |

This process equation system defines a process main as an internal choice between a process extend  $\rightarrow$  main and FAR. The latter is a process reference defined by the second equation of the system. The former is a prefix process, i.e., the process fires an event extend and behaves then as the main process again. The FAR process contains a sequential composition of two sub-processes, where the first is an interleaving of InitialState0 and InitialState1. The process Checked is defined as external choice: the process either receives a fail event from its environment and then behaves as process REC or it receives a pass and the main process is started again.

#### Semantics of CSP

There are three types of semantics that are commonly used to define the meaning of CSP processes: *operational semantics*, defining the semantics in terms of transition systems; *denotational semantics*, defining the semantics of a process in terms of a mapping into a semantical domain such that the semantics of a compound process can be computed by the semantics of its parts; and *algebraic semantics*, defining by algebraic laws which processes are meant to be equivalent. Roscoe [Ros98] gives an overview on these different semantical approaches to CSP.

In the class of denotational CSP semantics common representatives are the *trace*, the *stable-failures*, and the *failures-divergences* semantics. The former gives an abstract view to a process, because only sequences of events are considered, and the failures-divergences semantics gives the most accurate view, also including all dead-locks and divergences of a process. As we are basically interested in safety properties here, the trace semantics suffices for our needs.

Traces can easily be extracted from transition systems forming the operational semantics of CSP. It is defined as a *labelled transition system* (LTS)

$(Q, Events^{\tau \checkmark}, q_0, \longrightarrow),$

with a special event  $\checkmark$  representing the termination of a process, and an internal event  $\tau$  that is not visible from outside.  $Events^{\tau}$  is the set of events including  $\tau$ ,  $Events^{\checkmark}$  the set of events including  $\checkmark$ , and  $Events^{\tau \checkmark}$  the combination of both. The set Q contains all CSP processes, and  $q_0 \in Q$  is the initial process. The transition relation  $\longrightarrow$  is defined inductively over the structure of CSP processes by the following firing-rules.

$$\frac{}{\operatorname{Skip} \xrightarrow{\checkmark} \Omega} \qquad (\text{skip})$$

$$\frac{}{a \to P \xrightarrow{a} P} \qquad (\text{prefix})$$

$$\frac{P \xrightarrow{\tau} P'}{P \square Q \xrightarrow{\tau} P' \square Q} \qquad \frac{Q \xrightarrow{\tau} Q'}{P \square Q \xrightarrow{\tau} P \square Q'} \qquad a \in Events^{\checkmark} \quad (extchoice)$$

$$\frac{P \xrightarrow{a} P'}{P \square Q \xrightarrow{a} P'} \qquad \frac{Q \xrightarrow{a} Q'}{P \square Q \xrightarrow{a} Q'}$$

$$\frac{}{P \sqcap Q \xrightarrow{\tau} P} \qquad \qquad \frac{}{P \sqcap Q \xrightarrow{\tau} Q} \qquad (intchoice)$$

$$\frac{P \xrightarrow{b} P'}{P \parallel Q \xrightarrow{b} P' \parallel Q} \qquad \frac{Q \xrightarrow{b} Q'}{P \parallel Q \xrightarrow{b} P \parallel Q'} \qquad b \in Events^{\tau \checkmark} \land A \qquad parallel)$$

$$\frac{P \xrightarrow{a} P' Q \xrightarrow{a} Q'}{P \parallel Q \xrightarrow{a} P' \parallel Q'} \qquad \overline{\Omega \parallel \Omega \xrightarrow{\checkmark} \Omega} \qquad a \in A \setminus \{\tau\}$$

(parallel)

$$\frac{P \xrightarrow{\checkmark} P'}{P_{\ 9} \ Q \xrightarrow{\tau} Q} \qquad \qquad \frac{P \xrightarrow{a} P'}{P_{\ 9} \ Q \xrightarrow{a} P'_{\ 9} \ Q} \qquad \qquad a \in Events^{\tau} \qquad (seqcomp)$$

$$\frac{P \xrightarrow{\tau} P'}{P[R] \xrightarrow{\tau} P'[R]} \qquad \frac{P \xrightarrow{\checkmark} P'}{P[R] \xrightarrow{\checkmark} \Omega} \qquad \frac{P \xrightarrow{a} P'}{P[R] \xrightarrow{b} P'[R]} \qquad aRb \qquad (renaming)$$

$$\frac{P \xrightarrow{a} P'}{P \setminus B \xrightarrow{a} P' \setminus B} \qquad \qquad \frac{P \xrightarrow{b} P'}{P \setminus B \xrightarrow{\tau} P' \setminus B} \qquad \qquad a \notin B, b \in B \qquad (\text{hiding})$$

$$\frac{1}{X \xrightarrow{\tau} P} \qquad \qquad X \stackrel{\sim}{=} P \qquad (call)$$

$$\overline{\mu X \bullet F(X) \xrightarrow{\tau} F(\mu X \bullet F(X))}$$

(recursion)

We additionally use the convention that  $\Omega \setminus A = \Omega$  and  $\Omega[R] = \Omega$ .

We extend this single-step transition relation to a multi-step relation: The  $\tau$ -step transition relation  $P \stackrel{a}{\Longrightarrow} \overline{P}$  represents the  $\tau$ -closure of the single-step relation  $\stackrel{a}{\longrightarrow}$ , i.e.,  $P \stackrel{a}{\Longrightarrow} \overline{P}$  means that the LTS of P has a run from P to  $\overline{P}$

$$\langle a_0, a_1, \dots, a_i, a, a_{i+1}, \dots, a_n \rangle, \tag{2.1}$$

such that  $a_i = \tau$  holds for all  $i \in 0..n$ . The run (2.1) exists if there are transition steps  $P_i \xrightarrow{a_i} P_{i+1}$  for  $i \in 0..n$  and  $P_0 = P, P_{n+1} = \overline{P}$ . Furthermore, for a sequence of events  $w = \langle a_0, \ldots, a_n \rangle$  the multi-step transition relation  $P \xrightarrow{w} \overline{P}$  denotes the consecutive application of the single-step relation

$$P \stackrel{w}{\Longrightarrow} \overline{P} := P \stackrel{a_0}{\Longrightarrow} \circ \cdots \circ \stackrel{a_n}{\Longrightarrow} \overline{P}.$$

We use  $\implies^*$  to denote a sequence of arbitrary transition steps, i.e.,  $P \stackrel{w}{\implies} \overline{P}$  with arbitrary w.

With this multi-step transition relation, we can define the set of finite, prefix-closed traces of a process P by

$$traces(P) := \{ w \mid \exists Q : P \Longrightarrow Q \}.$$

Even though the systems we consider are reactive and usually have infinite behaviour, it is sufficient to include finite traces in the semantics, because the infinite traces can be computed from the set of all finite traces. This holds as long as no infinite branching processes are allowed [Ros98], which we explicitly exclude here.

#### 2.1.2. Object-Z

Object-Z [Smi00] is an object-oriented extension for the mathematical Z notation that has been developed mainly in the 1980s [Spi92]. It was standardised in 2002 [ISO02]. Z provides a notation for logical operators, sets, relations, and, based on this, a mathematical toolkit containing Z definitions for common mathematical operators and expressions like  $\cup, \cap, \subseteq, \emptyset$ , and notation for natural numbers and integers as well as sequences. One of the most obvious features of the Z notion is the use of a specific schema notation to structure a specification into smaller pieces. To give an example, the schema

| _ Train                                     |

|---------------------------------------------|

| $maxbd, maxcd, maxspd, ma, pos: \mathbb{R}$ |

| maxbd > 0                                   |

| maxcd > 0                                   |

| maxspd > 0                                  |

describes (a part of) the state space of a simple train control system: it declares three real-valued variables that need all to be larger than 0 and the variables ma and pos. The lines below the horizontal dash contain a predicate that has to be valid for the declared variables (the predicates in each line are connected by conjunction). Such a schema defines the set of all mappings from names (maxbd, maxcd, maxspd, ma, and pos) to values from the corresponding domain ( $\mathbb{R}$ ). These mappings are called *bindings*, written

$\langle maxbd == 3.2, maxcd == 2.5, maxspd == 500, ma == 1000, pos == -1.7 \rangle$

which is a valid binding for the schema above. Schemas can also be written in a condensed form, e.g., the *Train* schema can also be defined by

Train ==

[maxbd, maxcd, maxspd, ma, pos :  $\mathbb{R}$  | maxbd > 0  $\land$  maxcd > 0  $\land$  maxspd > 0].

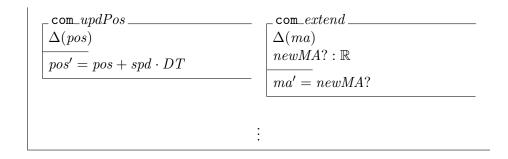

Variables are also used in *decorated* form with the standard decorations ', !, and ?. A *primed* variable x' denotes the state of the variable x after an operation, while ! and ? distinguish output and input variables, respectively. For instance, the operation schema

| extend              |  |  |

|---------------------|--|--|

| $\Delta(Train)$     |  |  |

| $newMA?:\mathbb{R}$ |  |  |

| 1 1/10              |  |  |

| ma' = newMA?        |  |  |

declares an input variable newMA? of type real and sets the new value of variable ma to the value of this input variable. The  $\Delta$ -expression in the first line introduces the symbols from the schema *Train*. Additionally, primed versions of all symbols of the *Train* schema are introduced such that ma' is actually declared for the *extend* operation.

#### Z Syntax

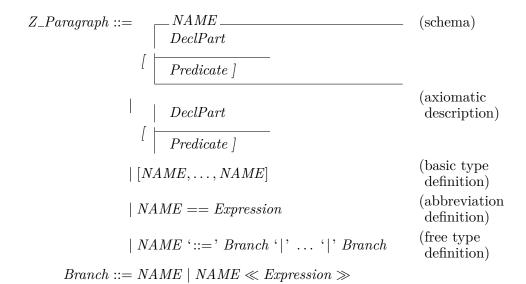

The basic building blocks in Z are paragraphs comprising the already introduced schemas, axiomatic descriptions, basic type definitions, abbreviation definitions, and

free type definitions:

Axiomatic descriptions introduce possibly constrained global variables, and basic type definitions allow for introducing identifiers for new types. Moreover, abbreviations can be defined, e.g.,  $Position == \mathbb{R}^+$  declares a new type Position. Finally, free types can be declared in a BNF syntax.

DeclPart is a declaration of the shape  $NAME_1 : TYPE_1, \ldots, NAME_n : TYPE_n$ . A Predicate is a Z expression that evaluates to true or false and comprises the standard operators from predicate logic,  $\land, \lor, \Rightarrow, \Leftrightarrow$  and quantifications

For instance, monotonicity of a function  $f : \mathbb{R} \to \mathbb{R}$  is defined in Z syntax by

$\forall x, y : \mathbb{R} \mid x \le y \bullet f(x) \le f(y).$

To avoid unnecessary mixing of syntactic constructs, we will use the notation of Z for predicates throughout this document.

**Remark 2.1.2 (Booleans and reals in Z).** Note that we follow the approach of Hoenicke with respect to the Boolean type  $\mathbb{B}$ . The type  $\mathbb{B}$  is often useful but not directly declared in the Z standard. Nevertheless, as explicated in [Hoe06],  $\mathbb{B}$  can easily be defined as abbreviation in standard Z syntax, so we consider  $\mathbb{B}$  as given. Analogously, the type  $\mathbb{R}$  is also not defined in the mathematical toolkit of the Z standard. We do not explicitly give an axiomatisation of real numbers in terms of a Z specification and instead refer to existing works on this [Art96, OB97, Toy98].

#### Z Semantics

The Z ISO standard [ISO02] defines the semantics of Z expressions as the set of possible values for all named symbols. The following symbols are used to describe the Z semantics:  $\mathbb{U}$  is the universe of all semantical values for Z expressions,  $\mathbb{W}$  is a set of subsets of  $\mathbb{U}$  for expressions that are not generic, and *Model* : *NAME*  $\Rightarrow$  U assigns values to symbols, where *NAME* is the set of all possible named Z symbols, and  $\Rightarrow$  denotes a finite partial function. With these basic elements, the semantical relations on Z terms are defined:

- $\llbracket Paragraph \rrbracket^{\mathcal{D}} \in Model \leftrightarrow Model$  assigns a meaning to paragraphs with the intuition that a paragraph declaring or restricting Z symbols relates an input model to a model that is extended according to the paragraph.

- $[Predicate]^{\mathcal{P}} \in \mathbb{P}Model$  assigns a set of valid models to a predicate.

- $\llbracket Expression \rrbracket^{\mathcal{E}} \in Model \to \mathbb{W}$  assigns a meaning to Z expressions, i.e., for a given model of the symbols from the expression, the expression is evaluated to a value from the semantical domain  $\mathbb{W}$ .

#### **Object-Z**

Object-Z (OZ) has been developed by Graeme Smith [Smi92, Smi00] to facilitate object-oriented modelling with a Z-based language. Thus, it incorporates the standard concepts of object-orientation like classes, objects, inheritance, and polymorphism. Beyond that, OZ is a conservative extension of Z such that all Z specifications are also valid OZ specifications.

To give an example of the main OZ construct, a class specification, we extend the *Train* example from the beginning of this section:

|                                    | Init                     |

|------------------------------------|--------------------------|

| $pos, spd: \mathbb{R}$             | maxcd = 110              |

| $ok, ebApplied : \mathbb{B}$       | maxspd = 10              |

| $ma, bd: \mathbb{R}$               | maxbd > 0                |

| $maxbd, maxcd, maxspd: \mathbb{R}$ | ma - pos > maxbd + maxcd |

This class *Train* (which is not completely presented here) describes the state space of *Train* objects together with possible operations on the state space, as well as all allowed initial values of attributes. The state space is defined with a so-called *state schema*, that defines, similarly to a standard Z schema, real-valued variables *pos* and *spd* representing the position and speed values of a train, some Boolean attributes *ok*, *ebApplied* etc. The schema marked with **Init** contains a predicate, defining initial values of the class attributes. The named schemas **com***updPos* and **com***extend* are the operations of the class, which change the state space. The use of such operations is the only way to change the state space of the class. For example, the operation  $com_updPos$  defines how the position variable *pos* is updated (*DT* is the length of the time interval from the last position update). Analogously to standard Z schemas, the  $\Delta$ -expression is used to introduce the primed version of *pos*, i.e., a (primary) variable can only be changed if it occurs in the  $\Delta$ -list of an operation. The **com***extend* schema additionally declares an input variable *newMA*?.

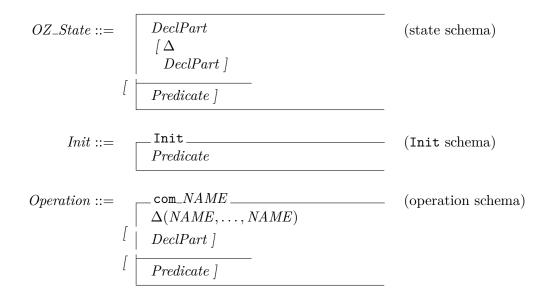

The syntax of state schema, Init schema, and operation schema is defined by:

#### 2.1.3. Duration Calculus

The Duration Calculus (DC) is an interval based dense real-time logic that was introduced in the early 1990s by Zhou Chaochen, C.A.R. Hoare, and A.P. Ravn [ZHR91] as part of the ProCoS project [HHF<sup>+</sup>94]. With DC formulae, properties over the duration of states in given time intervals can be formulated. The textbook [ZH04] gives a general overview on theoretical results on the DC. The following sections explicate syntax and semantics of DC.

#### **DC Symbols**

The syntax of DC is built on the following set of symbols.

- Observables  $X \in Obs$ . Observables (or state variables) are time-dependent variables having a finite domain, denoted  $D_X$  for an observable X. We use continuous time as time domain:  $Time == \mathbb{R}^+$  (for DC with discrete time see, e.g., [ZH04]).

- Functions  $f : \mathbb{R}^n \to \mathbb{R}$  and predicate symbols  $p : \mathbb{R}^m \to \mathbb{B}$ .

- Time-independent variables Vars.

These symbols are interpreted by the following mappings:

• The semantics of an observable X is a mapping from time into the data domain of the observable

$$\mathcal{I}[\![X]\!]: Time \to D_X,$$

called *interpretation*. The mapping  $\mathcal{I}[\![X]\!]$  is required to have finite variability, i.e., in every finite time-interval a state is not changed infinitely often.

• Function and predicate symbols are interpreted by corresponding functions

$$f: \mathbb{R}^n \to \mathbb{R} \text{ and } \widetilde{p}: \mathbb{R}^m \to \mathbb{B}.$$

We always interpret the arithmetical function symbols +, -, \*, / and relations  $<, \leq, =, \geq, >$  by their standard meaning.

• Global variables are interpreted by valuations

$\mathcal{V}(x) \in \mathbb{R}.$

The set of all valuations is denoted by Val.

#### State Assertions

State assertions (also state expressions) describe the state of the system at a given point in time, and they are defined by the following grammar:

$StateExpr ::= 0 \mid 1 \mid X = d \mid \neg StateExpr \mid (StateExpr \land StateExpr),$

where  $d \in D_X$ . The values 0 and 1 represent the Boolean constants true and false (for the purpose of the definitions of this section, we identify  $\mathbb{B}$  with the set  $\{0, 1\}$ ). The remaining Boolean connectives like  $\lor, \Rightarrow$  are considered as abbreviations.

The semantics of state assertions, which are also time-dependent, is given by the inductively defined extension of interpretations  $\mathcal{I}$  from observables to state assertions,  $\mathcal{I}[StateExpr]: Time \to \mathbb{B}.$