FAKULTÄT II – INFORMATIK, WIRTSCHAFTS- UND RECHTSWISSENSCHAFTEN DEPARTMENT FÜR INFORMATIK

# An Automated Semantic-Based Approach for Creating Task Structures

Dissertation zur Erlangung des Grades eines Doktors der Ingenieurwissenschaften

vorgelegt von

Dipl.-Inform. Matthias Büker

### Gutachter:

Prof. Dr. Werner Damm Prof. Dr. Martin Fränzle

Tag der Disputation: 04. Februar 2013

# © 2013 by Matthias Büker

Author's address: Matthias Büker

OFFIS

Escherweg 2

D-26111 Oldenburg

Germany

$\hbox{E-Mail:}\quad \hbox{matthias.bueker@offis.de}$

matthias.bueker@gmx.net

# **Danksagung**

Zunächst möchte ich meinem Doktorvater Prof. Dr. Werner Damm sowohl für die fachliche Betreuung meiner Arbeit, die vielen wertvollen Anregungen und die Stellung anspruchsvoller Herausforderungen als auch für die persönlichen Gespräche danken.

Zudem danke ich der Prüfungskommission bestehend aus dem Vorsitzenden Prof. Dr. Ernst-Rüdiger Olderog, den Gutachtern Prof. Dr. Werner Damm und Prof. Dr. Martin Fränzle sowie Dr. Sibylle Fröschle für ihre Bereitschaft meine Arbeit zu begutachten. Insbesondere danke ich Prof. Dr. Martin Fränzle, dass er trotz der unglücklichen Umstände bereit war an meiner Disputation teilzunehmen.

Des Weiteren geht ein ganz großer Dank an meinen "Sparringpartner" Dr. Ingo Stierand, der immer für Fragen und Diskussionen zur Verfügung stand und bereit war große Teile meiner Arbeit Probe zu Lesen. Weiterer Dank gebührt Tayfun Gezgin, der insbesondere bei den formalen Teilen der Arbeit als weiterer Probeleser eine große Hilfe war sowie Günter Ehmen und Matthias Stasch, die mich beim Vorbereiten meiner Evaluation unterstützt haben. Ebenso danke ich Jan-Patrick Osterloh für die Betrachtung meiner Arbeit aus einem anderen Forschungsblickwinkel, um insbesondere die einleitenden Passagen verständlicher zu gestalten.

Ein besonderer Dank gilt auch meinem Gruppenleiter der Forschungsgruppe EEA am OFFIS, Dr. Stefan Henkler, der mir vor allem in der "heißen" Phase immer den Rücken frei gehalten hat um meine Arbeit fertig stellen zu können. Ich danke auch allen weiteren aktuellen und ehemaligen Mitgliedern der Gruppe EEA, die mir ein angenehmes und diskussionsfreudiges Arbeitsumfeld geboten haben bestehend aus Raphael Weber, Philipp Reinkemeier, Eike Thaden, Sunil Malipatlolla, Maike Rosinger, Stefanie Schlegl, Alexander Stühring und Guilherme Baumgarten. Ich danke auch allen Kollegen aus den benachbarten Gruppen HDM, SAV-RSM, SAV-DAT und HCD vom OFFIS sowie den Bereichen "Sicherheitskritische Eingebettete Systeme", "Hybride Systeme" und "Eingebettete Hardware/Software Systeme" der Universität Oldenburg für spannende Seminare, Klausurtagungen, Vorträge und Diskussionen. Ein großer Dank geht auch an alle, die an meinem tollen Doktorhut mitgearbeitet haben!

Einen weiteren Dank möchte ich aussprechen an meinen ehemaligen Gruppenleiter Prof. Dr. Alexander Metzner, der mich besonders in der Anfangsphase der Arbeit bei der Themenfindung und Entwicklung der Grundideen unterstützt hat.

Nicht zuletzt möchte ich meinen Eltern und ganz besonders meiner wundervollen Frau Mirja für ihre mentale und emotionale Unterstützung insbesondere in der nervenbeanspruchenden Endphase der Arbeit danken. Ohne Dich hätte ich das vermutlich nicht durchgestanden. Danke!

# Zusammenfassung

Bei der Entwicklung von sicherheitskritischen eingebetteten Systemen müssen verschiedenste Aspekte berücksichtigt werden, um die Korrektheit des Systems nachzuweisen. Neben der rein funktionalen Korrektheit müssen solche Systeme auch Realzeiteigenschaften erfüllen, die typischerweise in so genannten End-to-End Deadlines ausgedrückt werden. Eine End-to-End Deadline fordert, dass bestimmte Ereignisse die im System beobachtet werden können innerhalb eines definierten Zeitintervalls auftreten. Dazu müssen alle Berechnungs- und Kommunikationsprozesse die für das Auftreten dieser Ereignisse notwendig sind innerhalb dieser Zeitspanne ausgeführt werden. Um solche Zeitanforderungen zu verifizieren sind verschiedene Techniken verfügbar bestehend aus formalen analytischen Methoden wie beispielsweise der Scheduling-Analyse oder Berechnungsmethoden wie Model-Checking. Um diese Methoden anwenden zu können, werden die Softwareanteile des Systems typischerweise als Tasknetzwerk dargestellt. Ein Tasknetzwerk ist ein gerichteter Graph bestehend aus Knoten die Anwendungsprozesse (Tasks) repräsentieren und Kanten die Abhängigkeiten zwischen Prozessen beschreiben.

In der industriellen Praxis gibt es eine Lücke zwischen der Spezifikation von Modellen durch einen Entwickler mittels eines Modellierungswerkzeugs wie MATLAB Simulink und der Darstellung als Tasknetzwerk, wie es für die Analyse von Zeiteigenschaften benötigt wird. Einerseits muss der Entwickler manuell entscheiden welche Teile des Modells zu einem Task zusammengefasst werden sollen und auf der anderen Seite muss die Semantik des Spezifikationsmodells bei der Erstellung des Tasknetzwerks erhalten bleiben. Andernfalls ist nicht sichergestellt, dass eine Analyse von Zeiteigenschaften tatsächlich das spezifizierte System überprüft. Hinzu kommt, dass in Werkzeugen wie Simulink keine Hardware modelliert und daher auch keine Allokation einzelner Softwareelemente auf Ausführungsressourcen wie Prozessoren betrachtet wird.

Der in dieser Dissertation vorgestellte Ansatz zur Erzeugung von Task-Strukturen (Task Creation) bildet den ersten Teil eines Prozessframeworks zur Untersuchung des Entwurfsraums eingebetteter sicherheitskritischer Systeme. Dieses Framework umfasst den gesamten Entwicklungsablauf, angefangen bei der Spezifikation von neuen Funktionen eines Fahrzeugs in Form von Simulinkmodellen, bis hin zu deren verteilter Ausführung auf hierarchischen elektronischen Hardwarearchitekturen. Bei der Task Creation wird in einem ersten Schritt aus einem gegebenen Simulinkmodell automatisch ein Tasknetzwerk abgeleitet, welches die partielle Ordnung von Blockausführungen erhält. Um diese Klasse von Modellen repräsentieren zu können, wird der Formalismus der Tasknetzwerke zu so genannten Funktionsnetzwerken erweitert.

Da ein aus Simulink gewonnenes Funktionsnetzwerk jedoch unausgewogen ist hinsichtlich seiner Knotengewichte im Sinne von Rechenintensität, werden in einem zweiten Schritt Knoten zu Tasks verschmolzen mit dem Ziel die so genannte Kohäsion

zu minimieren. Dieses Optimierungsmaß definiert, dass sich Knoten mit einer hohen Kommunikationsintensität anziehen und Knoten mit hohen Knotengewichten abstoßen. Das Ziel ist es Tasks mit sehr kleinen Gewichten zu vermeiden, um die Zahl der Taskwechsel zu reduzieren und die Kommunikation zwischen Tasks zu minimieren was die Busse der Hardwarearchitektur potentiell entlastet. Um die Korrektheit der Taskstruktur zu gewährleisten werden formale Kompositionsoperationen zum Verschmelzen von Knoten in einem Funktionsnetzwerk definiert. Für jede Operation wird nachgewiesen, dass diese die Semantik des Spezifikationsmodells im Sinne der Kausalität von Block- beziehungsweise Knotenausführungen erhält.

# **Abstract**

For the design of safety-critical embedded systems, many different aspects have to be considered to guarantee the correctness of the system. Besides functional correctness, these systems also have to meet real-time constraints expressed in terms of end-to-end deadlines. End-to-end deadlines claim that certain system events must occur within a given time interval. This means that all involved computation and communication processes have to be finished within this time bound. To verify such time bounds, different techniques may be used, such as scheduling-analysis as an analytical method, and model-checking as a computational method. For this step, the software parts of the model are typically represented as a task network. A task network is a directed graph of task nodes representing application processes, and edges indicating dependencies between processes.

In practice, there is a gap between the specification model a designer creates in high level modeling tools like MATLAB Simulink, and the task network representation used for timing analysis. On the one hand, the designer has to decide manually which parts of the model should form a task, and, on the other hand, semantics of the specification model has to be preserved when creating the task network. Otherwise, it cannot be assured that the timing analysis really verifies the specified system. Additionally, tools such as Simulink abstract from any concrete target hardware architecture and how the different software parts are mapped to hardware resources for execution.

The approach proposed in this PHD-thesis is called *task creation* and forms the first part of a design space exploration framework for safety-critical embedded systems. This framework addresses the complete design flow from specification models of new automotive features captured in Simulink to their distributed execution on hierarchical bus-based electronic architectures. During task creation, in a first step, a task network is derived automatically from a given Simulink model by preserving the partial order of block executions. To be able to represent Simulink models, the formalism of task networks is extended to so-called *function networks* offering more expressiveness.

As the obtained network is typically unbalanced in the sense of computational node weights, in a second step, nodes are merged to form application tasks following an optimization metric called *cohesion*. This metric is defined such that nodes are attracted by high communication density and repelled by high node weights. The goal is to reduce task switching times by avoiding too lightweight tasks and to relieve the bus by keeping inter-task communication low. To obtain tasks correctly, we define formal composition operations for merging nodes in a function network. For each operation, we prove that it preserves specification semantics in terms of causality of block and node executions, respectively.

# **C**ontents

| 1 | Intr | oduction                                     | 1    |

|---|------|----------------------------------------------|------|

|   | 1.1  | Overview and Goals                           | 2    |

|   | 1.2  | Concept and Approach                         | 5    |

|   | 1.3  | Outline                                      | 7    |

| 2 | Bas  | ics                                          | 9    |

|   | 2.1  | General Definitions and Notations            | 9    |

|   | 2.2  | Timed Languages and Timed Automata           | 10   |

|   | 2.3  | Event Streams and Event Models               | 13   |

|   |      | 2.3.1 Event Models                           | 14   |

|   |      | 2.3.2 AND- and OR-Operations on Event Models | 15   |

|   | 2.4  | Task Networks                                | 17   |

|   | 2.5  | MATLAB Simulink                              | 18   |

| 3 | Fun  | ction Networks                               | 21   |

|   | 3.1  | Event Patterns                               | 26   |

|   |      | 3.1.1 Definition of Event Patterns           | 27   |

|   |      | 3.1.2 Properties and Operations              | 30   |

|   | 3.2  | Function Network Definition and Properties   | 36   |

|   |      | 3.2.1 Basic Function Networks                |      |

|   |      | 3.2.2 Extended Function Networks             |      |

|   |      | 3.2.3 Properties of Function Networks        | 47   |

|   | 3.3  | Semantics of Function Networks               |      |

|   |      | 3.3.1 Causality and Timing Patterns          | 49   |

|   |      | 3.3.2 Basic Function Network Components      | 56   |

|   |      | 3.3.3 Extended Function Network Components   |      |

|   | 3.4  | Boundedness and Event Pattern Propagation    |      |

|   |      | 3.4.1 Event Pattern Propagation              | 83   |

|   |      | 3.4.2 Boundedness                            |      |

|   | 3.5  | Summary and Related Work                     |      |

| _ | _    |                                              |      |

| ļ |      |                                              | 103  |

|   | 4.1  | Formal Semantics for Simulink Models         |      |

|   |      | 4.1.1 Timed Synchronous Block Diagrams       | -108 |

### Contents

|     | 4.1.2 Execution Semantics for Simulink Models 4.2 Translating Simulink                                                                                                                                                                                                                             | 117<br>124                             |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|

| 5   | Task Creation  5.1 Cohesion and Weights  5.2 Formal Composition Operations and Semantics Preservation  5.2.1 Merging nodes  5.2.2 Elimination of Local Data Nodes  5.2.3 Elimination of Self-Activations  5.3 Task Creation Algorithm  5.4 Case Study and Evaluation  5.5 Summary and Related Work | 147<br>149<br>153<br>159<br>168<br>173 |  |  |  |

| 6   | Design Space Exploration  6.1 Overview of Design Space Exploration Process 6.1.1 Global Analysis 6.1.2 Local Analysis and Backtracking 6.2 On the Role of Task Creation 6.3 Case Study and Evaluation 6.4 Summary                                                                                  | 187<br>189<br>190<br>193               |  |  |  |

| 7   | Conclusion                                                                                                                                                                                                                                                                                         | 197                                    |  |  |  |

|     | Proofs for Function Networks  A.1 Proofs for Event Patterns                                                                                                                                                                                                                                        | 210<br>214<br><b>217</b>               |  |  |  |

|     | B.1 Proofs for Translation                                                                                                                                                                                                                                                                         |                                        |  |  |  |

| С   | Proofs for Task Creation C.1 Proofs for Formal Composition Operations                                                                                                                                                                                                                              | <b>231</b> 231                         |  |  |  |

| Inc | dex                                                                                                                                                                                                                                                                                                | 235                                    |  |  |  |

| Lis | et of Figures                                                                                                                                                                                                                                                                                      | 237                                    |  |  |  |

| Lis | List of Tables                                                                                                                                                                                                                                                                                     |                                        |  |  |  |

| Bil | bliography                                                                                                                                                                                                                                                                                         | <b>241</b>                             |  |  |  |

# 1. Introduction

This work is settled in the area of the design and analysis of safety-critical embedded systems with the focus on real-time properties. Embedded systems are computer systems that are part of other larger systems or devices with a certain purpose, and are found in multiple domains, such as aviation, automotive or automation engineering. Typical tasks of embedded systems are to control and monitor such systems, which may include also mechanical parts.

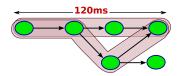

Because embedded systems often control safety-critical tasks - in particular in the aviation and automotive domain - the verification of certain properties concerning safety, functionality and timing is key to make them available for the productive use. Functional and timing properties are usually strongly related because the correct functionality is only assured if timing constraints are met. Typical timing constraints are end-to-end deadlines between specific system events. For example, the actuator triggering the airbags of a car has to be activated within a time bound of 15 to 30 milliseconds after a collision has been detected by a crash sensor to guarantee that the airbags inflate in time to protect the passengers. To verify timing constraints, there exist different approaches, which can be divided into analytical methods as scheduling analysis [66], and computational methods as model-checking [19]. To be able to apply those analysis techniques, the software parts of the system are modeled as a process or task network [24]. In general, a task network is a graph where nodes represent application tasks implemented as executable program code. Tasks are connected by edges modeling dependencies between tasks. For modeling communication, task networks may also contain signals, which transmit data between tasks. The occurrence of events in task networks is typically described by event streams and event models [73, 40].

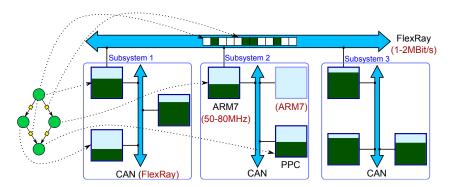

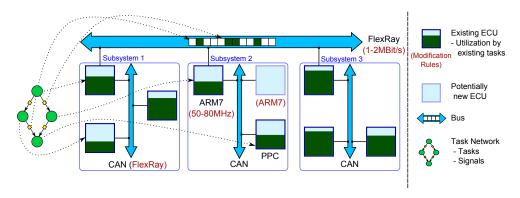

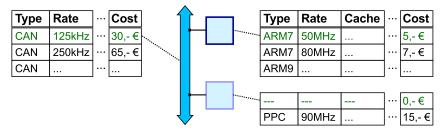

The design of safety-critical embedded systems involves several phases, like definition of requirements, system specification, and implementation of the system on a hardware platform. This work is part of a framework [10, 11] that aims at automating significant parts of the design flow in a typical scenario for embedded application development in the automotive domain. It was developed within the Transregional Collaborative Research Center "Automatic Verification and Analysis of Complex Systems" (SFB/TR 14 AVACS). In this framework, a common hierarchical bus-based target architecture from the automotive domain is considered, where electronic control units (ECUs) are clustered in subsystems. Subsystems are connected by a backbone TDMA (Time Division Multiple Access) bus. In Figure 1.1 an example of such an architecture is depicted with three subsystems connected by a FlexRay backbone bus, where each subsystem contains a set of ECUs, which communicate via a local CAN bus.

Motivated by the iterative design process in industrial practice, we assume that this architecture is already pre-deployed with the functionality of an existing set of applications in terms of software tasks. This is sketched in Figure 1.1, where a part

#### 1. Introduction

Figure 1.1.: Distributed Hardware Architecture

of the pre-deployed task network is shown on the left. The dotted arrows indicate the allocation of tasks to processors and signals to buses. The utilization of the existing processors, induced by pre-deployed tasks, is indicated by partially filled boxes. For example, in *Subsystem 1*, the ECU at the top left is filled with around 70% utilization.

For the next generation of the system, a new customer feature should be implemented. This might be, for example, a new driver assistance system. For the feature specification of embedded systems in the industrial practice, there exist a number of high-level modeling tools for the individual domains. For this work, we will focus on the automotive domain, where Simulink is a standard tool for system modeling.

To offer sufficient computational capacity for the new feature, the hardware architecture may be modified by adding new ECUs, or by replacing existing ones by more powerful ECU types. In Figure 1.1, allowed modifications are shown in parenthesis. For example, the left ECU of Subsystem 2 is an ARM7 processor that may be clocked with 50 to 80 MHz. The empty box on the top right of the same subsystem indicates the possible addition of another ARM7 ECU. Each modification induces costs depending on the added or replaced ECU type. The overall goal of the framework is to find a conservative cost-optimized extension of the existing architecture to implement the new feature while meeting all timing constraints.

### 1.1. Overview and Goals

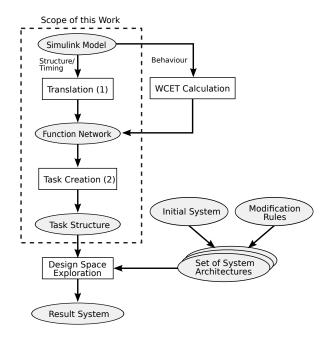

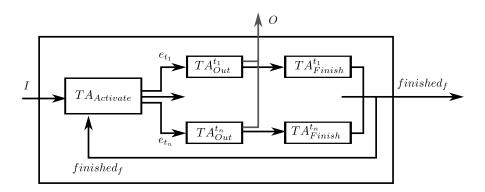

The approach presented in this work forms the front-end of the design space exploration framework shown in Figure 1.2, where the scope of this work is indicated by a dashed rectangular box. In this first part, a task structure is automatically derived from a Simulink specification model of a new feature. In the succeeding *Design Space Exploration* (DSE), this task structure should be deployed to an existing system in terms of software tasks allocated to a distributed hardware architecture.

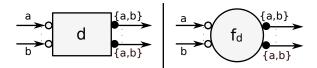

The first goal of this work is to define a *Translation (1)* of the structure of a Simulink model and its timing properties into a task network. To be able to represent the semantics of Simulink models, the task network formalism is extended to a so-called function network. For each block of the Simulink model, worst case execution times

Figure 1.2.: Overview of Design Space Exploration Framework

(WCETs) are estimated based on generated code. These WCETs are used to estimate computational weights for the obtained function network nodes. Please note, that WCET calculation itself is not part of this work.

One scientific challenge for this part is to assure the correctness of the translation from a synchronous language like Simulink to an asynchronous task network formalism meaning that same input values lead to same output values. This is done by showing that the execution semantics of Simulink in terms of the partial order of block executions is preserved such that signals are computed in a valid order. The correct behavior of single blocks is ensured by generating code using existing code generators. Another challenge is to define an extension of the task network formalism that enables to represent the execution semantics of Simulink models and to prove the relevant properties needed to show the correctness of the translation. Because we aim at an implementable system, also the question of boundedness is highly relevant meaning that the software system is implementable with a finite set of (memory) resources. Thus, a class of function networks is defined where boundedness is decidable and which is sufficient to represent Simulink models.

Because the network obtained from a Simulink translation typically consists of a large number of nodes with unbalanced computational weights and a high amount of communication, the second goal of this work is to derive a reasonable task structure from the translated function network. To realize this, in the so-called *Task Creation* (2) step, nodes are iteratively merged into tasks by formal composition operations on function networks. The scientific challenges in this part can be divided into two

#### 1. Introduction

categories: First, a methodology and optimization metric for merging nodes needs to be developed with the aim to derive a task structure that is suitable to be mapped to a pre-deployed distributed hardware architecture as it is considered in the design space exploration. Second, it needs to be assured that the execution semantics of the specification model is preserved by the formal composition operations to merge function nodes. This is done by showing that the partial order of Simulink block executions is not violated by any merging operation.

The resulting task structure serves as input to the design space exploration process, which has the goal to find a feasible task allocation on the distributed architecture with minimum costs. The set of available system architectures is comprised of the initial system and a set of allowed modification rules. However design space exploration is no conceptional part of this work, it is used to evaluate the proposed approach in the overall context of the framework.

Overview of Related Work A lot of work has been done concerning the translation of Simulink into other synchronous or asynchronous languages. In [81], Simulink models are translated to Lustre to partition the generated code into modules that are executed on different processors communicating via a time-triggered bus. Here, the focus lies on efficiently generating modular code and separating it into different modules respecting a global partial order. In our approach, we use existing code generators to generate code for Simulink blocks and thus the question of optimal code generation is not in the scope of this work but can be considered as supplementary.

A further work was presented in [80], where a synchronous model is implemented on a loosely time-triggered architecture. The authors only consider single-rate models while for our approach the semantic preservation for multi-rate models is one major part. Furthermore, they cannot always guarantee that no data is lost because they allow Simulation steps of Simulink to overlap. Similar problems occur in [71], where tasks are identified manually from a Simulink model and scheduled in a fixed-priority preemptive scheduling. In our translation, we follow the Simulink simulation semantics and forbid overlapping executions by defining respective end-to-end deadlines to assure data consistency.

In [6] and [7], an overview is given on the basic idea of synchrony and the most important synchronous languages and it is discussed how to translate a synchronous language to an asynchronous one in general. In contrast to these approaches, we do not aim at representing the complete functional behavior of a synchronous model in our translation to an extended task network model. Instead, we assure the correctness of our translation by preserving the partial order of signal updates induced by block executions. The functional correctness of the computations of single blocks is assured by applying existing code generators to generate code for those blocks.

An approach comparable to the idea of task creation was proposed in [23], where an optimization of the multi-task implementation of Simulink models with real-time constraints is considered. The optimization goal is to reduce the use of rate transition blocks between different synchronous sets to minimize buffering and latencies. The tasks for the scheduling analysis are either determined by the synchronous sets or are also part of the optimization problem. Beside the optimization goal, the main difference to our work is the target hardware in terms of a single processor, while we consider a distributed bus-based architecture.

Another work from Kugele et al. [46] is also based on synchronous languages and presents a way to deploy clusters in terms of tasks on a multi-processor platform. This allocation process is completed by a scheduling analysis. The authors also raise the question of how to generate clusters of nodes to form tasks but assume that this is a decision that is taken manually by the user.

A more detailed discussion of related work can be found in the summary of each main chapter of this work.

## 1.2. Concept and Approach

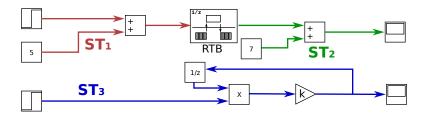

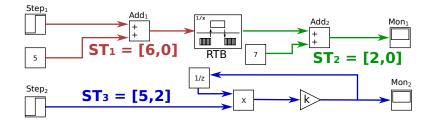

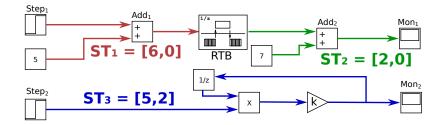

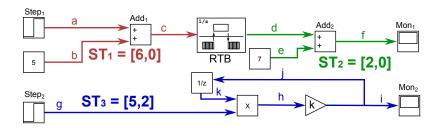

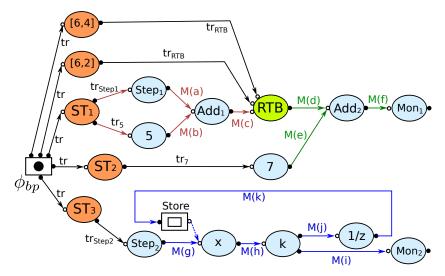

In Simulink, the functionality of a system is modeled in terms of synchronous block diagrams, where each block fulfills a specific function. Blocks are connected by signals delivering values from one block to another. A block may first be executed if all its input signals have been updated by the execution of preceding blocks. Sample times are used to determine at which points in time a block is executed, and consist of a period and an initial phase offset. Synchronous sets are defined as a set of connected blocks with the same sample time. Blocks of different synchronous sets may also be connected by rate transition blocks if their periods are integer multiples. Those blocks ensure that the respective signal values are available if the succeeding block is executed and that the partial order is guaranteed if both connected blocks are executed in one simulation step. To structure the model, subsystems may be used, which are hierarchical blocks containing other blocks and signals. In Figure 1.3, an example of a Simulink block diagram is shown consisting of three synchronous sets with sample times  $ST_1$ ,  $ST_2$ , and  $ST_3$ . A rate transition block named RTB connects the synchronous sets with sample times  $ST_1$  and  $ST_2$ .

Figure 1.3.: Example of a Simulink Block Diagram

In Simulink, it is possible to model discrete systems in terms of the actual embedded controller as well as continuous systems, which may be used to model the environment. Simulink models can be simulated to evaluate the functionality of the system. During simulation, block execution in Simulink does not consume time. Instead, simulation is performed in discrete steps for discrete controller models. Thus, it is implicitly assumed that in each step all needed blocks can be executed to deliver results at their

#### 1. Introduction

output ports. Obviously, the assumption of instant block execution cannot hold for any implementation because task execution on an ECU always consumes time.

This leads to a gap between specification models, as they are designed in Simulink, and task networks, which are the basis for timing analysis. To close this gap, it first needs to be assured that a Simulink model can be correctly translated into a task network. Because we aim at analyzing timing properties, we abstract from the concrete functional behavior of blocks. Instead, we define a translation to be correct if it preserves the partial order of Simulink block executions and satisfies the assumption that all blocks are executed within one simulation step.

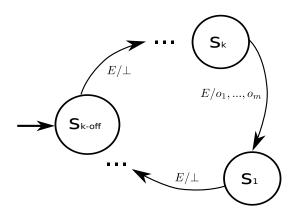

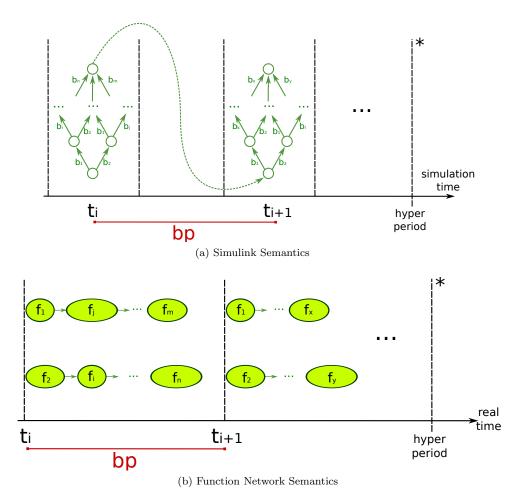

To be able to represent the semantics of a Simulink model in terms of synchronization of multiple input signals and consistent behavior of blocks with different sample times, we define an extended task network called function network, which allows more expressiveness. In a function network, tasks are denoted as function nodes and edges as channels. As a first extension, we introduce AND-activation (synchronization) of incoming channels of function nodes to translate blocks with multiple input signals. To model rate transition blocks that convert from a slower to a faster period, we further define OR-activation (superposition) to model the additional activations. A rate transition from a faster to a slower block must only write each n'th signal update, where n is the integer multiple of the respective sample times. To realize this, we define an internal state transition system for function nodes, which allows to produce different output events depending on the state and received input events.

As a further block type, in Simulink data store memory blocks are used to model data exchange between blocks without inducing a partial order relation. To allow the modeling of such data dependencies, we define special communication nodes called data nodes. Data nodes may be of different types as shared memory and FIFO buffers. To be able to show preservation of certain semantic properties during translation and task creation, semantics of function networks needs to be defined formally. This is done by defining atomic components in terms of timed automata that are composed to function network elements like function nodes and channels.

Based on the function network formalism, we define a translation from Simulink specification models, where blocks are translated to function nodes and signals to channels. Because the hierarchy of the model in terms of subsystems does not influence the semantics but is only used to structure the model, we translate the flattened block diagram. To show that the partial order of block executions is preserved in the function network translation, we relate Simulink signal updates to function network events. Furthermore, it has to hold that all block executions of a simulation step are finished before the next simulation step starts.

After the translation, the process continues with the decision which parts of the specification model should form a task. The code generator of Simulink offers a multitask implementation, where all blocks with the same sample time are realized as one task. However, this is not necessarily the best choice if tasks should be allocated to a distributed hardware architecture with pre-deployed tasks. In this scenario, ECUs usually have a high utilization by the existing tasks in order to use hardware resources efficiently. Thus, tasks that need a high amount of computational capacity might not be deployable to any existing ECU. Hence, we need to find a partitioning of the

specification functionality into a set of tasks with "reasonable" computational needs. To describe the computational capacity a task needs for its execution, we introduce node weights. Thus, one goal for task creation is to avoid tasks with too large weights. On the other hand, task weights should also not be too small. If we would, for example, assume each atomic block of a Simulink model to be represented as one task, this would lead to a very high number of tasks with comparatively small weights. If such tasks were deployed to an ECU, this would lead to frequent task switching, also denoted as thrashing. In summary, task weights should be balanced to avoid both too heavy and too lightweight tasks.

Another important aspect is that usually many blocks of a Simulink model are connected by signals leading to a high amount of communication. If such a fine-granular task network would be spread over a distributed hardware architecture, this would lead to a high bus utilization. But buses are often the bottleneck of distributed systems and can hardly be upgraded, or only with very high costs. Thus, a further goal for task creation is to find a task set with a minimum inter-task communication to relieve the buses. To cover all these issues, we define an optimization metric for task creation called *cohesion*. It defines that nodes are attracted by edges with a high communication density and repelled by high node weights. This leads to minimizing inter-task communication and balancing task weights as well.

To perform task creation, an algorithm is defined that partitions function nodes into task sets while minimizing cohesion. This is done in two steps, where first an initial solution is created that is improved in a second step by a variant of the Kernighan-Lin heuristic [43]. The result of the algorithm is a set of node partitions, where each partition represents a task. To finish task creation, all function nodes within the same partition are merged to one node in the function network. For this, we define a set of formal composition operations. A merging of two nodes means that they will be considered as one task and thus will be executed on one computation resource. This leads to less task activations, and thus also to less task switches. As for the translation from Simulink, we also show for the task creation operations to preserve the original execution semantics of the specification model.

### 1.3. Outline

First, we introduce in Chapter 2 the fundamentals that are needed for this work in terms of formalisms like timed automata, task networks, and tools like Simulink. In Chapter 3, we define function networks as an extension of task networks. To be able to show semantics preservation of the Simulink translation and task creation process, we define causality and timing properties of function networks that should be preserved. Furthermore, we show for a class of function networks that boundedness is decidable by propagation event models through the network.

In Chapter 4, we define a translation of Simulink block diagrams into function networks and show that this translation preserves the partial order semantics of Simulink. In Chapter 5, we present the task creation approach starting with defining the optimization metric cohesion and weights of function nodes and channels. For merging

### 1. Introduction

nodes, we define formal composition operations and show that they preserve the specification semantics in terms of causality. Furthermore, an algorithm is proposed to perform node partitioning and the approach is evaluated with a case study.

In Chapter 6, we shortly present the design space exploration process of the framework and discuss the role of task creation. Furthermore, we evaluate the task creation approach by applying the design space exploration with different task networks of the same specification model. Finally, in Chapter 7, we conclude this work by summarizing and discussing the results with respect to the defined goals.

# 2. Basics

In the context of this work, we make use of some formalisms and tools, which are introduced in this chapter. We start with general definitions and notations in Section 2.1. In Section 2.2, we define timed languages and timed automata, which build the base to define semantics of function networks.

To describe the occurrence of events in a function network, event streams and event models are used, which are presented in Section 2.3. In Section 2.4, task networks are introduced which can be considered as predecessor of function networks. Finally, in Section 2.5, we introduce the high level modeling tool suite MATLAB Simulink, which we assume as starting point for our design process.

### 2.1. General Definitions and Notations

First, we define the following notations for sets of numbers:

- $\mathbb{N}_0$ : Set of natural numbers including zero.

- N<sup>+</sup>: Set of natural numbers except zero.

- $\mathbb{R}$ : Set of real numbers.

- $\mathbb{R}_0^+$ : Set of positive real numbers including zero.

- $\mathbb{R}^+$ : Set of positive real numbers except zero.

- $\mathbb{Q}_0^+$ : Set of positive rational numbers including zero.

- $\mathbb{Q}^+$ : Set of positive rational numbers except zero.

Because execution times of tasks and function nodes, respectively, will be defined as intervals of natural numbers, we define the following operations on intervals.

**Definition 2.1.1 (Interval Arithmetic)** Let [a,b] and [c,d] be intervals with  $a,b,c,d \in \mathbb{N}_0$ . We define addition, minimum and maximum of intervals as follows:

- Addition: [a, b] + [c, d] := [a + c, b + d]

- $Minimum: \min([a, b], [c, d]) = [\min(a, c), \min(b, d)]$

- *Maximum*:  $\max([a, b], [c, d]) = [\max(a, c), \max(b, d)]$

A basic concept to show semantics preservation of the Simulink translation is the partial order relation. Based on [82], we define a partial order as follows:

**Definition 2.1.2 (Partial Order)** A (strict) partial order  $PO(\Sigma)$  is a binary relation < over a set  $\Sigma$  that is irreflexive, antisymmetric, and transitive, i.e.  $\forall a, b, c \in \Sigma$ :

- (1)  $\neg (a < a)$  (irreflexive)

- (2)  $a < b \land b < a \implies a = b \ (antisymmetric)$

- (3)  $a < b \land b < c \implies a < c \ (transitive)$

We write  $(a,b) \in PO(\Sigma)$ , if a < b where a is called predecessor of b, and b is called successor of a.

# 2.2. Timed Languages and Timed Automata

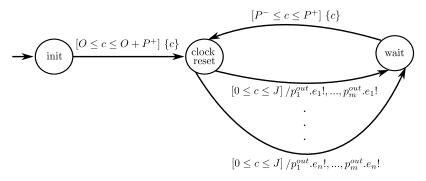

Timed automata are an extension of finite state machines with time and were defined by Alur and Dill [3]. Timed automata offer a set of special variables named clocks, which increase uniformly when time passes. Based on values of clocks, guards of transitions allow to define constraints when a transition may be taken. Clocks may also be reset to zero by transitions.

Furthermore, invariants allow to constrain how long an automaton is allowed to stay in a specific state. States are often referred to as *locations* because the actual state of a timed automaton is determined by the location *and* the value of all clocks.

The language of timed automata is defined in terms of timed words forming a timed language. Based on [3] and [85], we define timed words and timed languages as follows:

**Definition 2.2.1 (Timed Word and Timed Language)** Let  $\Sigma$  be a set of events, and let  $\mathbb{T} = \mathbb{R}_0^+$  be a time domain. An infinite sequence  $\omega = (\sigma_i, t_i)_{i \in \mathbb{N}^+}$  where  $\sigma_i \in \Sigma$ ,  $t_i \in \mathbb{T}$  is a timed word if and only if:

- 1.  $\forall i < j : t_i \leq t_j \ (Monotonicity)$

- 2.  $\forall c \in \mathbb{T} \ \exists i : c \leq t_i \ (Progress)$

Let  $\Omega(\Sigma, \mathbb{T})$  be the set of timed words over  $\Sigma$ . Then  $L \subseteq \Omega(\Sigma, \mathbb{T})$  is a timed language over  $\Sigma$ . For a timed word  $\omega = (\sigma_i, t_i)_{i \in \mathbb{N}^+}$ , we also write  $(\sigma_1, t_1)(\sigma_2, t_2)...(\sigma_i, t_i)...$ . For each element of a word  $\omega$  we write  $(\sigma_i, t_i) \in \omega$ .

For system modeling, network of timed automata are defined, which are used in tools like UPPAAL [5, 49]. In such a network, a set of timed automata communicate via synchronization channels, where a sender channel is denoted as c! and its respective receiver channel as c?. Furthermore, urgent synchronization channels are defined, where delays must not occur if a synchronization transition on an urgent channel is enabled. Edges using urgent channels for synchronization cannot have clock guards. Also locations may be urgent, meaning that time is not allowed to pass when the system is in such a location. In committed locations it additionally has to hold that

they are left with the next transition. If more than one automaton is in a committed location, this has to hold for at least one of the committed locations.

We define clock constraints and clock valuations as done in [33] as follows:

**Definition 2.2.2 (Clock Constraint [33])** Let C be a set of clocks. A clock constraint is defined by the syntax

$$\varphi ::= c_1 \sim t \mid c_1 - c_2 \sim t \mid \varphi \wedge \varphi,$$

where  $c_1, c_2 \in C$ ,  $t \in \mathbb{Q}_0^+$  and  $\sim \in \{\leq, <, =, >, \geq\}$ . The set of all clock constraints over the set of clocks C is denoted by  $\Phi(C)$ .

**Definition 2.2.3 (Clock Valuation [33])** Let C be a set of clocks. Clock valuation is a function

$$\nu: C \to \mathbb{R}_0^+$$

assigning each clock in C a non-negative real number.

We denote  $\nu \models \varphi$  the fact that a clock constraint  $\varphi$  evaluates to true under the clock valuation  $\nu$ . We use  $0_C$  to denote the clock valuation  $\{c \mapsto 0 \mid c \in C\}$ , abbreviate the time shift by  $\nu + d := \nu(c) + d$  for all  $c \in C$ , and clock resets by  $\nu[\varrho \mapsto 0]$  with  $\nu[\varrho \mapsto 0](c) = 0$  if  $c \in \varrho$ , and  $\nu[\varrho \mapsto 0] = \nu(c)$  else, where  $\varrho \subseteq C$ .

For the definition of timed automata, we rely on the definition of [85], while we additionally allow the set of locations to be infinite.

#### Definition 2.2.4 (Timed Automaton)

A Timed Automaton (TA) is a tuple  $A = (L, L^c, l^0, \Sigma, \Sigma^u, C, Inv, R)$  where

- L is a non-empty set of locations,  $L^c \subseteq L$  is the set of committed locations and  $l^0 \in L$  is an initial location,

- $\Sigma$  is a finite alphabet of channels, inducing the action set  $\Sigma_{?!} = \{a? \mid a \in \Sigma\} \cup \{a! \mid a \in \Sigma\} \cup \{\tau\}$ , where  $\tau$  denotes internal actions,

- $\Sigma^u \subseteq \Sigma$  is the set of urgent channels,

- C is a finite set of clocks.

- $Inv: L \to \Phi(C)$  is a mapping which assigns an invariant to each location,

- $R \subseteq L \times \Sigma_{?!} \times \Phi(C) \times 2^C \times L$  is a set of transitions. A tuple  $t = (l, \sigma, \varphi, \varrho, l')$  represents a transition from location l to location l' annotated with the action  $\sigma$ , the constraint  $\varphi$  and a set of clocks  $\varrho$  which have to be reset.

For t we also write  $l \xrightarrow{\sigma,\varphi,\varrho} l'$ .

As introduced in [85], we define a mapping chan "such that each element of the action set is mapped to the corresponding channel, e.g.,  $chan(\sigma!) = chan(\sigma?) = \sigma$ . If  $chan(\sigma) \in \Sigma^u$ , then  $\varphi = true$  i.e. no guards are allowed on transitions synchronizing on urgent channels" [85].

#### 2. Basics

Following [85], we can model a system by a network of timed automata with pairwise disjoint clock sets as follows: "A network of n timed automata is denoted by  $A_1||...||A_n$  and modeled by a timed transition system. During computation, each automaton is in a specific location. The locations of all automata are collected in a control vector denoted by  $l = (l_1, ..., l_n)$ . A change from location  $l_i$  to  $l'_i$  of the ith automaton of a given network is denoted by  $l[l_i/l'_i]$  "[85]. A timed transition system modeling a network of timed automata is defined in [85] as follows:

**Definition 2.2.5 (Timed Transition System [85])** Let  $A_i$  be a network of timed automata with  $A_i = (L_i, L_i^c, l_i^0, \Sigma_i, \Sigma_i^u, C_i, Inv_i, R_i)$ ,  $i \in \{1, ..., n\}$  and pairwise disjoint sets of clock variables. The semantics of such a network is defined in terms of a timed transition system denoted as

$$\mathcal{T}(A_1||...||A_n) = (\Sigma_{out}, Conf, Conf^0, C, \rightarrow)$$

where

- $\Sigma_{out} = \bigcup_{i=1}^{n} (\Sigma^{u}(A_i) \setminus \bigcup_{j=1, j \neq i}^{n} \Sigma^{u}(A_j))$  the so-called open synchronization channels of the network, inducing the action set  $\Sigma_{?!,out} = \{a? \mid a \in \Sigma_{out}\} \cup \{a! \mid a \in \Sigma_{out}\}$

- $Conf = \{(l, \nu) \mid l_i \in L_i \land \nu \models \bigwedge_{j=1}^n Inv_j(l_j)\}$  is the set of configurations,

- $Conf^0 = (l^0, 0_C)$ , where  $l^0 = (l_1^0, ..., l_n^0)$  is the initial location vector and  $0_C$  is the initial clock valuation, i.e.  $\{c \mapsto 0 \mid c \in C\}$ ,

- $C = \bigcup_{i=1}^{n} C_i$  is the set of clock variables,

- $\rightarrow \subseteq Conf \times (\bigcup_{j=1}^n \Sigma_{?!,j} \dot{\cup} \mathbb{R}_0^+ \cup \{\tau\}) \times Conf$  is the transition relation. A transition  $((l,\nu),\lambda,(l',\nu'))$ , also denoted by  $(l,\nu) \xrightarrow{\lambda} (l',\nu')$ , has one of the following types.

- Delay transitions  $(l,\nu) \xrightarrow{t} (l,\nu+t)$  with  $t \in \mathbb{R}_0^+$  can occur, if  $\nu+t \models \bigwedge_{j=1}^n Inv_j(l_j)$ . Moreover, neither an urgent channel is active nor an automaton is in a committed state, i.e.

- (i) there exist no  $i, j \in \{1, ..., n\}$  and  $\sigma \in \Sigma^u$  with  $(l_i, \sigma!, \varphi_i, \varrho_i, l_i') \in R_i$  and  $(l_j, \sigma?, \varphi_j, \varrho_j, l_j') \in R_j$

- (ii) there exist no  $i \in \{1, ..., n\}$  with  $l_i \in L_i^c$ .

- Local transitions  $(l, \nu) \xrightarrow{\lambda} (l', \nu')$  with  $\lambda \in \Sigma_{?!,out} \cup \{\tau\}$  can occur, if for some  $i \in \{1, ..., n\}$  it holds that  $(l, \lambda, \varphi, \varrho, l') \in R_i$ , such that  $\nu \models \varphi$ ,  $l' = l[l_i/l_i']$ ,  $\nu' = \nu[\varrho_i \mapsto 0]$  and  $\nu' \models Inv_i(l_i')$ . Furthermore it holds that if  $l_k \in L_k^c$  for some  $k \in \{1, ..., n\}$  then  $l_i \in L_i^c$ .

- Internal transitions  $(l, \nu) \stackrel{\tau}{\to} (l', \nu')$  can occur, if for some  $i, j \in \{1, ..., n\}$  with  $i \neq j$  and  $\sigma \in \Sigma_i \cap \Sigma_j$  there are transitions  $(l_i, \sigma!, \varphi_i, \varrho_i, l'_i) \in R_i$  and  $(l_j, \sigma?, \varphi_j, \varrho_j, l'_j) \in R_j$  such that  $\nu \models \varphi_i \wedge \varphi_j$ ,  $l' = l[l_i/l'_i][l_j/l'_j]$ ,  $\nu' = \nu[\varrho_i \mapsto 0, \varrho_j \mapsto 0]$  and  $\nu' \models Inv_i(l'_i) \wedge Inv_j(l'_j)$ .

- Furthermore it holds that if  $l_k \in L_k^c$  for some  $k \in \{1,...,n\}$  then  $l_i \in L_i^c$  or  $l_j \in L_j^c$ .

Following [85] "given a configuration  $(l, \nu)$  of a network of n timed automata M, we say M can move to configuration  $(l', \nu')$  by synchronizing on  $\sigma \in \Sigma_{?!,out}$  after delay  $d \in \mathbb{R}_0^+$ , denoted by  $(l, \nu) \xrightarrow{\sigma} (l', \nu')$ , if and only if there exists a sequence

$$(l,\nu)\xrightarrow{\rho_1}(l_1,\nu_1)\xrightarrow{\rho_2}\dots\xrightarrow{\rho_n}(l_n,\nu_n)\xrightarrow{\sigma}(l',\nu'), n\in\mathbb{N}_0,$$

with  $\rho_i \in \mathbb{R}_0^+ \cup \{\tau\}$ ,  $1 \le i \le n$ , such that  $\sum_{i=1}^n \rho_i = d$  "[85] where  $\tau + d = d$ . For the definition of the language of a timed transition system, we slightly differ from [85] and define the language also on internal symbols and not only on open synchronization channels as follows:

**Definition 2.2.6 (Language of TTS)** Let  $M = (\Sigma_{out}, Conf, Conf^0, C, \rightarrow)$  be a network of n timed automata. A finite sequence  $\bar{\gamma} = ((l_i, \nu_i), \lambda_i)_{0 \le i \le n}$  of pairs of configurations of M and actions  $\lambda_i \in \Sigma_{?!,out} \cup \mathbb{R}_0^+ \cup \{\tau\}$  for all  $0 \le i < n$  is called partial computation of M of length n if and only if  $((l_0, \nu_0), \lambda_0) = ((l^0, 0_C), \tau)$  and if adjacent pairs are consecutive, i.e.  $(l_i, \nu_i) \xrightarrow{\lambda_{i+1}} (l_{i+1}, \nu_{i+1})$  for  $0 \le i < n$ . An infinite sequence  $\gamma$  of pairs of configurations of M and actions is called computation of M if each prefix of  $\gamma$  is a partial computation.

We say a partial computation  $\bar{\gamma}$  computes the (finite) timed word  $\omega = ((\sigma_i)_{0 \le i \le n},$  $(t_i)_{0 \le i < n}$ ), denoted by  $M \xrightarrow{\omega \setminus n} (l', \nu')$ , if and only if there exists a configuration  $(\vec{l'}, \nu')$  of M such that  $(l^0, 0_C) \xrightarrow{\sigma'_0} \dots \xrightarrow{\sigma'_{n-1}} (l', \nu')$  with  $\sigma_i = chan(\sigma'_i)$  for all  $i \in \{0,...,n-1\}$ . We set  $t_{-1} = 0$  to uniformly cover the case i = 0.

The TTS M computes the timed word  $\omega$  if and only if it computes each prefix of  $\omega$ . The language L(M) of M is the set of timed words computed by M.

We apply two further extensions introduced for UPPAAL timed automata in [5, 49]. First, guards may be also defined over bounded integer variables, which are considered as part of the state space. Second, we allow broadcast channels where one sender c!synchronizes with an arbitrary number of receivers c?.

### 2.3. Event Streams and Event Models

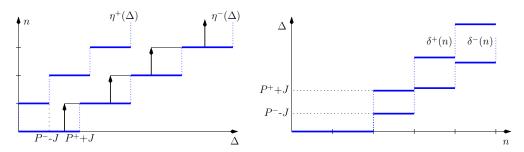

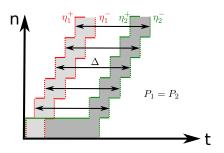

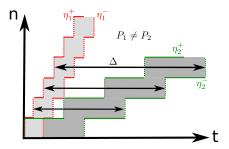

Event streams are used in real-time theory and in particular in scheduling analysis to describe the occurrence of task activations in terms of events within a specific time interval. They are defined by four characteristic functions: The  $\eta^-$  and  $\eta^+$  functions give for a specific time interval the minimum and maximum number of events that may occur i.e.,  $\eta^-(\Delta) = n$  means that within a time interval of  $\Delta$  at least n events may be observed. The  $\delta^-$  and  $\delta^+$  functions give for a specific number of events the minimum and maximum time distance where this number of events may occur. Hence,  $\delta^+(n) = \Delta$  means that the maximum time distance between n events is bounded by  $\Delta$ . According to [73], both the pair of  $\eta$  and  $\delta$  functions are each sufficient to represent the characteristics of an event stream because they can be derived from each other.

#### 2.3.1. Event Models

Based on event streams, event models were defined to represent a certain class of event streams. In [40, 66], Jersak and Richter describe an approach to perform compositional scheduling analysis using standard event models. The most common models are the strictly periodic event model and the periodic with jitter event model where activations may be delayed by a jitter. Jitter may also lead to overlapping invocations of events if it becomes greater than the period, which is known as burst.

The periodic event model with jitter was defined by Jersak in [40] as follows while we use slightly different notations to avoid ambiguities:

**Definition 2.3.1 (Periodic with Jitter Event Model)** Let  $Period \in \mathbb{R}^+$  be a period and  $Jitter \in \mathbb{R}_0^+$  be a jitter. Periodic event streams with jitter are defined as

$$\eta^{+}(t)_{P+J} = \left\lceil \frac{t + Jitter}{Period} \right\rceil$$

$$\eta^{-}(t)_{P+J} = \max\left(0, \left\lfloor \frac{t - Jitter}{Period} \right\rfloor\right)$$

<

An extension of this model was proposed in [24], where for the  $\eta^-$  and  $\eta^+$  functions different periods  $P^+$  and  $P^-$  are defined. Thus, the period may vary between these bounds. This additionally allows to model *sporadic* streams where a minimum interarrival time  $d^-$  between events is defined. This is realized by choosing  $P^+ = \infty$  and  $P^- = d^-$ .

The periodic/sporadic event model with jitter was defined in [24] as follows:

**Definition 2.3.2 (Periodic/sporadic Event Model with Jitter)** The periodic/sporadic event model with jitter is a function  $\mathcal{EM}: (\Sigma \times \mathbb{T}^3) \to 2^{\Omega(\Sigma)}$ , where  $\mathcal{EM}(e, P^-, P^+, J)$  characterizes the set of timed traces with occurrences of events e with lower and upper periods bounds  $P^- \in \mathbb{R}^+$ ,  $P^+ \in \mathbb{R}^+ \cup \{\infty\}$  and jitter  $J \in \mathbb{R}^+_0$  is defined for  $0 \le J < P^- \le P^+$  as

$$\eta^{+}(\Delta) = \left\lceil \frac{\Delta + J}{P^{-}} \right\rceil,$$

$$\eta^{-}(\Delta) = \max\left(0, \left\lfloor \frac{\Delta - J}{P^{+}} \right\rfloor\right)$$

<

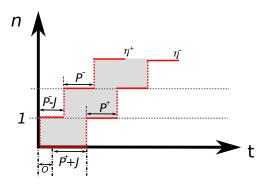

In Figure 2.1, the  $\eta$  functions for the periodic and sporadic event model are depicted on the left and the  $\delta$  functions on the right.

Another event model has been introduced by Thiele et al. in [78, 47], where a performance analysis technique is proposed that is based on a formalism named Real-Time Calculus (RTC). Here, so-called arrival curves are used to model the computation that is requested by a process. In the following we give the definition of arrival curves

Figure 2.1.: Periodic/Sporadic event stream model (Source: [24])

from [78, 47] while we differ from the original notation by denoting the minimum and maximum distance (period) between event occurrences as  $P^-$  and  $P^+$  instead of  $\delta^u$  and  $\delta^l$  (where  $P^- = \delta^u$ ,  $P^+ = \delta^l$ ).

**Definition 2.3.3 (Real Time Calculus (RTC) Arrival Curves)** In RTC an arrival curve is defined as upper and lower staircase function as follows:

$$\alpha^{u}(\Delta) := N^{u} + \left\lfloor \frac{\Delta}{P^{-}} \right\rfloor$$

$$\alpha^{l}(\Delta) := N^{l} + \left\lfloor \frac{\Delta}{P^{+}} \right\rfloor$$

describing traces which contain at least  $\alpha^l(\Delta)$  and at most  $\alpha^u(\Delta)$  event signals for any interval of length  $\Delta \in \mathbb{R}_0^+$ . The parameter  $N^u$  can be understood as burst capacity, which describes the number of events producible in zero time according to curve  $\alpha^u$ . The parameters  $P^-$  and  $P^+$  specify the minimum/maximum distance of two successive events. The absolute values of parameter  $N^l$  of the lower curve can be understood as the fictitious numbers of periods  $(P^+)$  before event emission has to be enforced every  $P^+$  time unit.

This model has some differences to the previous models because it does not define a jitter. But it also allows different periods  $P^-$  and  $P^+$  for the upper and lower curves and additionally defines initial values  $N^l$  and  $N^u$  for both curves. The initial value for the upper curve may be modeled by the model of Jersak as well by choosing a jitter greater than the period. Another difference is the definition of the  $\eta^+$  and  $\alpha^u$  function. If we assume Jitter=0 and  $N^u=1$  (which is implicitly the case in the model of Jersak), the value of  $\eta^+(k\cdot Period)$  is k in the model of Jersak and Richter, while in the RTC model  $\alpha^u(k\cdot P^-)$  is defined to be k+1. Thus, analysis results may differ depending on the utilized model.

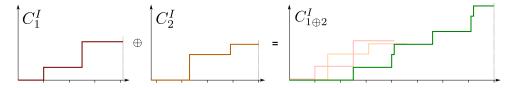

## 2.3.2. AND- and OR-Operations on Event Models

Jersak defined in [40] operations for the synchronization (AND) and superposition (OR) of event models where we focus again on the periodic event model with jitter.

#### 2. Basics

AND-activation of event streams occurs if a task needs multiple inputs to be activated leading to the need to synchronize all input streams and to buffer events until all synchronization partners have arrived. To ensure that an AND-activated task is ever activated these input buffers need to be bounded, which is assured for periodic event models with jitter if the period of all input models is the same. We will later prove in Section 3.1 that this is a sufficient and necessary condition to decide boundedness of buffers for periodic event models with jitter and an additional offset. According to Jersak [40], AND-activation of periodic event models with jitter is defined as follows:

**Definition 2.3.4 (AND-Activation - Periodic with Jitter)** AND-activation of n input event models described by the parameters  $(Period_i, Jitter_i)$  with  $Period_i = Period_j$  for all  $i, j \in \{1, ..., n\}$  is defined as the event model

$$(Period_{AND}, Jitter_{AND}),$$

where

$$Period_{AND} = Period_i$$

and  $Jitter_{AND} = \max_i \{Jitter_i\}.$

OR-activation of event streams describes that a task is activated if on any of its input streams an event occurs. This leads to a superposition of all input event models. According to Jersak [40], OR-activation of such event models is defined as follows:

**Definition 2.3.5 (OR-Activation - Periodic with Jitter)** OR-activation of n input event models described by the parameters  $(Period_i, Jitter_i)$  with  $i \in \{1, ..., n\}$  is defined as the event model

$$(Period_{OR}, Jitter_{OR}), where$$

- $Period_{OR} = \frac{1}{\sum_{i=1}^{n} \frac{1}{Period_i}}$

- $Jitter_{OR}$  is the minimum jitter which fulfills the following equations:

$$\left\lceil \frac{t + Jitter_{OR}}{Period_{OR}} \right\rceil \ge \sum_{i=1}^{n} \left\lceil \frac{t + Jitter_{i}}{Period_{i}} \right\rceil$$

$$\max\left(0, \left\lfloor \frac{t - Jitter_{OR}}{Period_{OR}} \right\rfloor\right) \le \sum_{i=1}^{n} \max\left(0, \left\lfloor \frac{t - Jitter_{i}}{Period_{i}} \right\rfloor\right)$$

$\Diamond$

In [40] it is shown that the minimum jitter values for the lower and upper curve are always identical. Furthermore, an approach is proposed to calculate such a minimum jitter by considering all constant segments of the upper curve for one macro period. The overall minimum jitter can then be determined as the smallest value which satisfies the equation for all constant segments.

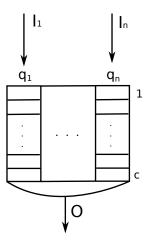

### 2.4. Task Networks

A task network is a common formalism to model the software parts of a system in performance and scheduling analysis of real-time systems. It is a graph formalism consisting of nodes that are referred to as tasks or processes, and edges between tasks. Edges typically model control-flow dependencies and thus also precedences between tasks. Task activations are usually modeled using event streams, which have been introduced in Section 2.3.

While there exist different variants of task networks, we rely on task networks as they have been defined in [24]. There, a task network is defined as a graph consisting of trigger nodes where events are produced, sinks where events are consumed, task nodes representing processes, and edges between tasks representing control-flow dependencies. Edges are sometimes also referred to as *signals*. Furthermore, tasks are annotated with response times and execution times, respectively. They are defined as an interval of a minimum and maximum time bound. Please note, that for this definition, the event model from Def. 2.3.2 is used.

**Definition 2.4.1 (Task Network [24])** A task network TN is a tuple  $(\Sigma, C, E)$  where  $\Sigma$  is a set of event labels,  $C = Q \cup T \cup S$ , Q is a set of triggers, T is a set of tasks, S is a set of sinks, and  $E \subseteq C \times \Sigma \times C$  is a set of edges. The components are defined as follows:

- A trigger  $q \in Q$  is a tuple  $(e, P^-, P^+, J, \pi_e^{out})$  where  $e \in \Sigma$ , and  $P^-, P^+, J \in \mathbb{T}$ .  $\pi_e^{out}$  is an event model, defined as  $\mathcal{EM}(e, P^-, P^+, J)$ .

- A task  $\tau \in T$  is a tuple  $(e, f, P^-, P^+, J, R^-, R^+, \pi_e^{in}, \pi_f^{out})$  where  $e, f \in \Sigma$ , and  $P^-, P^+, J, R^-, R^+ \in \mathbb{T}$ . The event model  $\pi_e^{in}$  is defined as  $\mathcal{EM}(e, P^-, P^+, J)$  and  $\pi_f^{out}$  is defined as  $\mathcal{EM}(f, P^-, P^+, J + R^+ R^-)$ .

- A sink  $s \in S$  is a tuple  $(e, P^-, P^+, J, \pi_e^{in})$  where  $e \in \Sigma$ , and  $P^-, P^+, J \in \mathbb{T}$ . The event model  $\pi_e^{in}$  is defined as  $\mathcal{EM}(e, P^-, P^+, J)$ .

TN has to satisfy the following constraints:

- (C, E) must be an acyclic graph.

- For each  $q = (e, P^-, P^+, J, \pi_e^{out}) \in Q$  there is at least one edge  $(q, f, c) \in E$  with  $c \in T$

- For each  $\tau=(e,f,P^-,P^+,J,R^-,R^+,\pi_e^{in},\pi_f^{out})\in T$  there is a unique edge  $(c,e,\tau)$  with  $c\in Q\cup T$  and at least one edge  $(\tau,g,d)\in E$  with  $d\in T\cup S$ .

- For each  $s=(e,P^-,P^+,J,\pi_e^{in})\in S$  there is a unique edge  $(c,e,s)\in E$  with  $c\in T$ .

- Components connected by an edge  $(c, e, d) \in E$  must be compatible, i.e., for  $\pi_c^{out} = \mathcal{EM}(e', P_c^-, P_c^+, J_c)$ , and  $\pi_d^{in} = \mathcal{EM}(e, P_d^-, P_d^+, J_d)$ , it must hold that  $[P_c^-, P_c^+] \subseteq [P_d^-, P_d^+]$ , and  $J_c \leq J_d$ .

Figure 2.2.: Example for a Task Network (Source: [24])

For this work, we will always refer to worst case execution times (WCETs) when reasoning about task runtimes instead of response times. This is due to the fact that we derive task networks from specifications in Simulink, where no hardware resources are available and thus no interaction of tasks on a shared resource is considered.

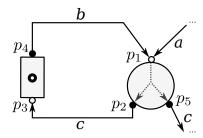

In Figure 2.2, a task network is shown, where tasks have already been deployed to a processor (CPU) or a bus. Tasks are depicted as white-filled circles with a label such as T1 and edges between them are drawn as directed arcs. The gray-shaped circles model the interface to the environment in terms of triggers and sinks. Trigger model inputs, where events are produced with a specific event model and sinks represent outputs, where events are consumed.

### 2.5. MATLAB Simulink

Simulink is a high level system modeling tool, which allows the modeling and simulation of dynamic systems from a multitude of domains including continuous and discrete systems. It is based on MATLAB, which is a numerical computing environment. Simulink also offers a framework for code generation named  $Embedded\ Coder$ . MATLAB, Simulink and Embedded Coder are distributed by MathWorks <sup>1</sup>. Another code generator for Simulink is TargetLink distributed by dSpace <sup>2</sup>.

In Simulink, systems are modeled in terms of block diagrams, where blocks represent specific functions and signals are used to connect output ports of one block with input ports of another block. Simulink offers a rich library of standard modeling blocks but also the possibility to create user-defined blocks such as so-called S-Functions. Block diagrams may be simulated to observe the system behavior. For simulation a solver needs to be chosen where different discrete and continuous solvers are available depending on the characteristics of the system. Timing characteristics of blocks are defined by  $sample\ times$ , which are defined by the user or by Simulink. Sample times can be also classified as either being discrete or continuous. Discrete sample times consist of a period per and an initial phase offset init. Thus, a block is executed in the simulation steps  $init, init + per, init + 2 \cdot per, \dots$ . For simulation, continuous sample times are transformed into discrete sample times depending on the simulation step size, which is determined by the chosen Simulink solver.

Discrete systems are, for example, used to model a controller that should be implemented on a hardware platform whereas continuous systems are typically used to

$<sup>^{1}</sup>$ www.mathworks.com

$<sup>^2</sup>$ www.dspace.com

Figure 2.3.: Example for a Simulink Block Diagram

model the environment of the discrete system. For this work, we only consider discrete systems. For discrete systems and a discrete solver with a fixed step-size, code may be produced by using code generators such as Embedded Coder or TargetLink.

In Figure 2.3, an example of a Simulink block diagram is shown. This model contains three different sample times that are denoted as  $ST_1$ ,  $ST_2$ , and  $ST_3$ . For example, sample time ST3 = [5, 2] means that those blocks are executed first in simulation step 2 and afterwards periodically with a period of 5 leading to the steps 2,7,12,17,... A set of connected blocks with the same sample time is referred to as a synchronous Assuming a fixed-step solver, blocks of different synchronous sets may only be connected by a signal if a rate transition block is inserted in between. This block guarantees a deterministic data transfer by holding the last value of a preceding producer block and offering it to a succeeding consumer block if needed. The concrete behavior depends on whether the producer or the consumer block has the larger period. If the consumer block runs with a smaller period (meaning a higher rate), it is executed in more steps than the producer block. Thus, the signal value of the producer block must be available also when this block is not executed. In the other case, where the producer block is executed more often, it is not necessary to store the value, but it must be guaranteed that the order of block executions is preserved when both blocks are executed in a simulation step.

Simulink also allows to model loops. For this work, we only allow models with so-called non-algebraic loops meaning that each loop contains a delay block as e.g. a Unit Delay block. In Figure 2.3, the part with sample time  $ST_3$  contains a non-algebraic loop with a unit delay block denoted as 1/z. We also allow that the behavior of a block may be modeled by finite state machines by using Stateflow. Stateflow is integrated in Simulink and offers an environment to model so-called state charts.

# 3. Function Networks

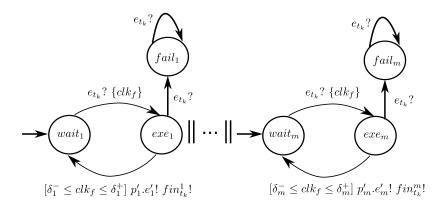

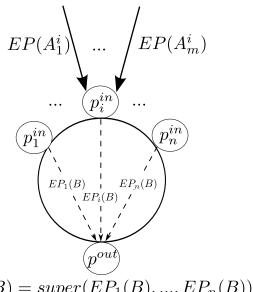

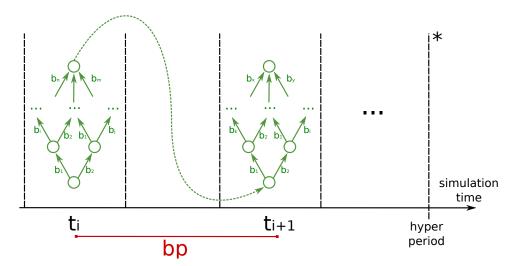

As formal base for the Simulink translation and task creation, an extended task network formalism called *function network* is introduced. To be able to show semantics preservation, formal semantics of function networks is defined and properties about causality and timing are derived that should be preserved when translating a Simulink model and performing merging operations. As a necessary condition to implement a system, also boundedness of function networks is discussed and a class of function networks is defined where boundedness is decidable.

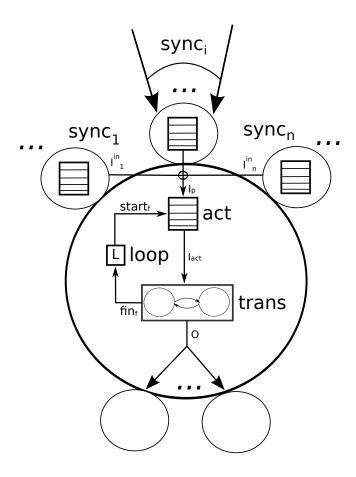

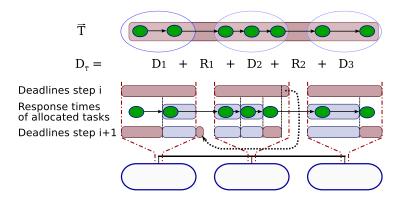

A function network is a graph that consists of nodes called function nodes, edges called channels and trigger nodes called event sources, and is an extension of the task network formalism presented in Section 2.4. In a task network, nodes represent tasks that are pieces of software in terms of executable code, which should be executed on a hardware processor. Tasks may have several properties, where from the real-time point of view the most interesting are the worst case execution time (WCET), the activation pattern describing when the task is triggered for an execution, and the (hard) deadline when this task has to finish its execution. Furthermore, there may exist end-to-end deadlines giving timing constraints over task chains. Deadlines and activation patterns are properties that originate from the system specification, which is given as a Simulink model for this work. Contrastingly, the worst case execution time depends on the software code of the task and the target processor where the task is executed. In the scenario we consider here, there exists a set of target processors and thus the WCET can be determined for each target processor, for example, by using aiT [30]. Thus, we get one WCET for each task and each target processor.

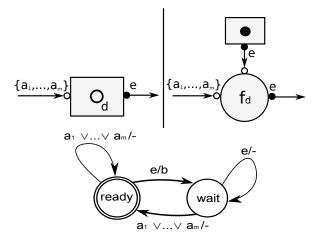

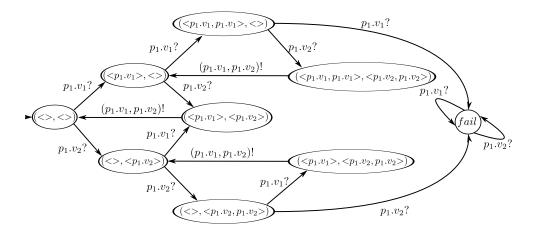

The need to extend the model of task networks has several reasons leading to different kind of extensions. First, it is often not sufficient to assume that a task is triggered by a single channel or trigger. In practice, we may have, for example, *synchronous* activations, which means that a task is only activated if on all its incoming edges a trigger event has occurred. This is typically the case in synchronous languages, such as synchronous block diagrams used in Simulink. Please note, that for synchronization, we always need a buffer to store events until all synchronization partners have arrived. Furthermore, there may be also overlapping activations, denoted as *superposition* meaning that a task may either be activated by a trigger event a or a trigger event b. We will need this kind of activation also when translating Simulink block diagrams to model rate-transitions between blocks with different sample times. A further need to represent superposition of task activations is the more general case, where a task is part of different task chains that are executed independently from each other.

In function networks, we introduce *input ports*, which represent activation points of function nodes and may have several incoming channels. To activate an input port on each channel an event is needed realizing a synchronization of these events. Super-

#### 3. Function Networks

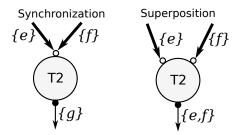

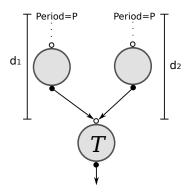

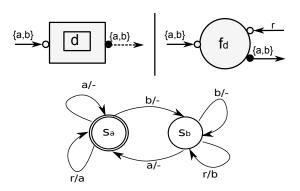

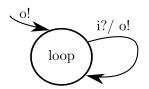

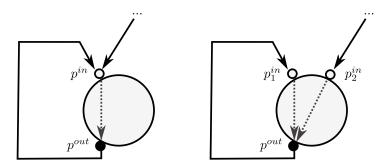

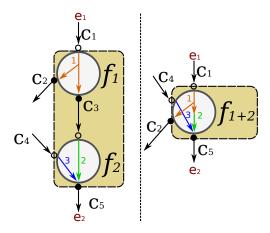

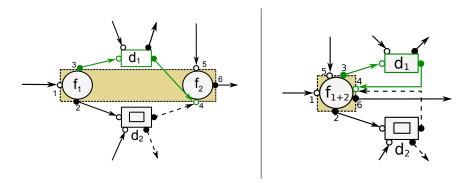

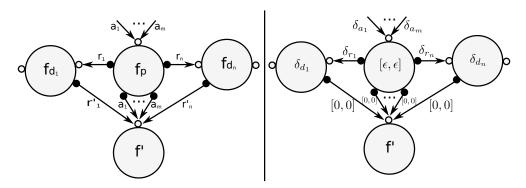

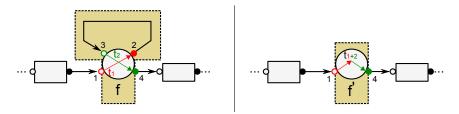

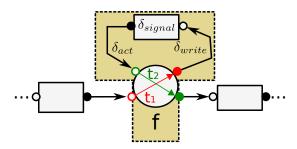

Figure 3.1.: Task Activation by Synchronization (AND) and Superposition (OR)

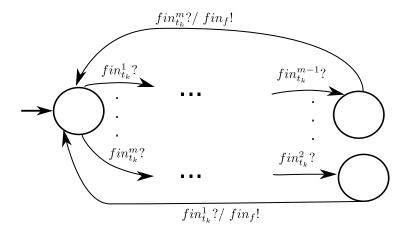

position may be modeled by a function node with multiple input ports, where each input port activation leads to an activation of the node. This kind of activations can already be found in existing task models as e.g. in [68]. To describe event occurrences at ports in a function network, we introduce *event patterns*, which are an extension of classic periodic event models [40].

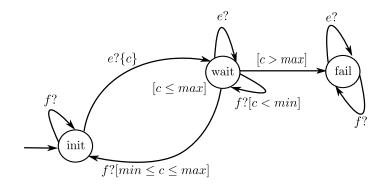

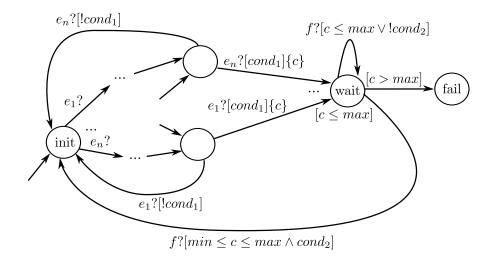

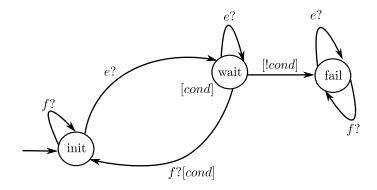

In Figure 3.1 on the left, an example for a synchronization is depicted. Task T1 receives events from two incoming channels that lead to the same input port (depicted as small circle). T1 is activated whenever an event e was received on the left channel and an event f was received on the right channel leading to an event g at the output port. On the right of Figure 3.1, an example for a superposition is shown. Task T2 is activated if an event e on the left channel e0 an event e1 at the right channel is received. The received event is forwarded to the output port.

Another important reason to extend task networks is the fact that the WCET of a task may depend on the input data it processes and on the internal state of the task, which may change due to previous executions. In classic task networks, the WCET of a task is a safe upper bound for all possible kinds of input data and internal state configurations. This often leads to over-approximations in timing analysis and thus possibly to a negative result in terms of a deadline violation although the assumed WCET will never be reached under specific input and state conditions. There already exist analysis approaches to cover these issues such as state-based scheduling [56].

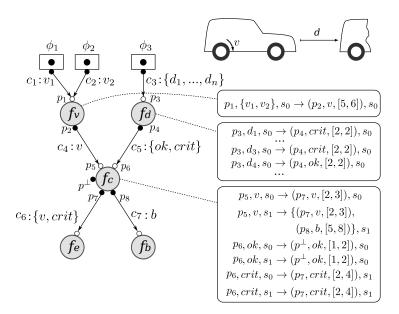

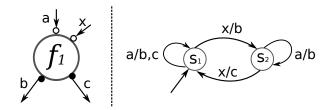

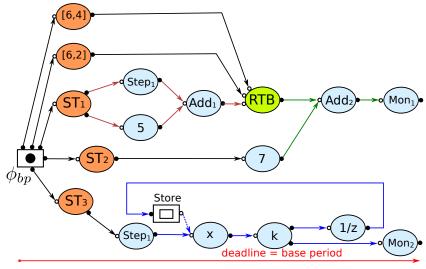

As an example, we could think of a simple adaptive cruise control (ACC) system equipped with speed sensors  $\phi_1$  and  $\phi_2$  and a distance sensor  $\phi_3$ , which measures the distance to preceding cars as depicted in Figure 3.2. The sensor values are aggregated by the tasks  $f_v$  (speed sensors) and  $f_d$  (distance sensor). The resulting values are forwarded to a controller task  $f_c$ , which decides whether it is necessary to initiate a braking action to avoid a collision. As long as the distance is not critical, denoted by the event ok, the task forwards the values to nodes of the car periphery via task  $f_e$ . This only needs a comparatively small execution time. If the distance to the vehicle ahead becomes critical, denoted by the event crit, a braking measure is initiated by an event b triggering task  $f_b$ . This deceleration process must be controlled leading to a mode change of the controller task involving a larger execution time. We will consider this example in more detail in Section 3.2.

If we were able to represent this kind of information in a task network model, this may reduce over-approximations in timing analysis and thus improve the quality of

Figure 3.2.: Simple Example of an Adaptive Cruise Control (ACC) System

the results. Thus, in design space exploration, task allocations may become feasible that would be rejected with classic task networks. This may lead to more possible solutions for task allocations and hence also to lower modification costs.

Accordingly, we extend the model of a task in a function network by introducing an internal state transition system that is sensitive to incoming data in terms of events and the internal state of the task. Each transition is annotated with a delay, which represents the worst case execution time for a specific input and state configuration assumed by the considered transition. Another extension is to allow transitions that produce events at different output ports with different delays leading to a set of delays per transition. Furthermore, we may observe different events on the same channel leading to different behavior of the function node. If we consider again the example of the ACC system, there may be two different events sent on the same channel to distinguish between sensor values below and above a certain threshold value denoting a critical distance.

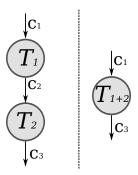

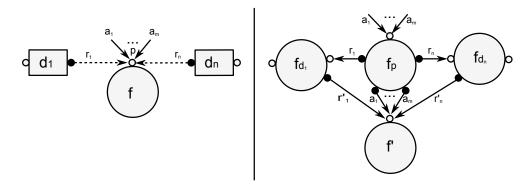

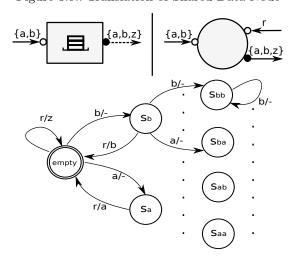

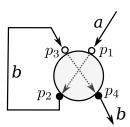

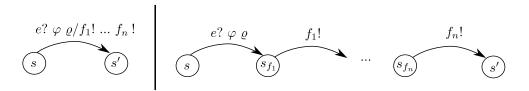

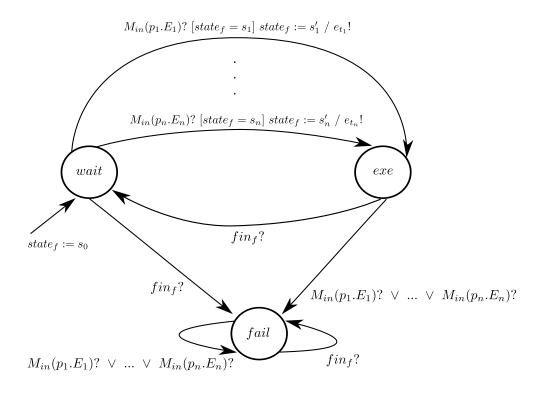

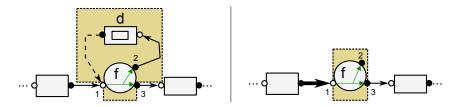

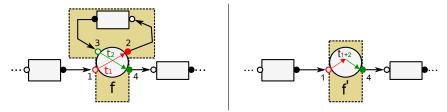

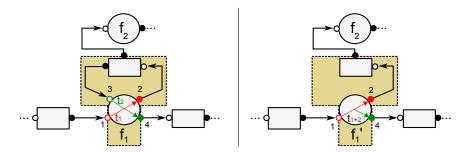

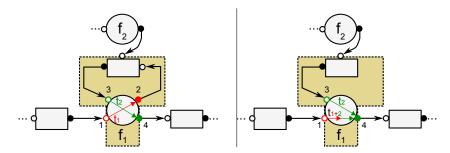

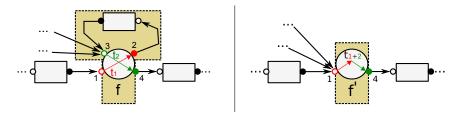

Another important reason to introduce internal state transition systems in task nodes arises from one of the essentials of this work: the merging of nodes. If nodes are merged to build a task, we need to deal with the question how this may be represented in the task network formalism. In doing so, we need to assure that we do not violate the semantics of the model in terms of causality of task executions and events. Thus, if we want to reason about what merging of nodes semantically means, we need to have some abstract representation of the behavior of the task. In Figure 3.3 on the left, an extract of a task network with two sequential tasks  $T_1$  and  $T_2$  is depicted where  $T_1$  has one outgoing channel triggering  $T_2$ , and  $T_2$  has no other incoming channels. For this simple case, it would be sufficient to say that merging  $T_1$  and  $T_2$  leads to a task

#### 3. Function Networks

Figure 3.3.: Merging Example for a Simple Task Chain

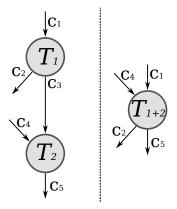

$T_{1+2}$  that has all incoming channels of  $T_1$  and whose WCET is the sum of the single WCETs of  $T_1$  and  $T_2$ . The result is shown in Figure 3.3 on the right. But as soon as  $T_1$  has more than one outgoing channel, or  $T_2$  has more than one incoming channel, we get into difficulties to represent the behavior correctly as illustrated in Figure 3.4. If we would perform the merging in the same manner as for the previous case, the events on outgoing channels of  $T_1$  not leading to  $T_2$  would automatically be delayed, because the WCET of  $T_{1+2}$  is the sum of the single WCETs. But actually, the output of  $T_1$  would be available already after the execution of the program code that belongs to  $T_1$ . Thus, we need the possibility to annotate different WCETs for different outputs of a task to represent delays correctly.

Figure 3.4.: Merging Example for a Complex Task Chain

If  $T_2$  has more incoming channels than the one from  $T_1$ , as  $c_4$  in Figure 3.4, these channels would also be input channels of  $T_{1+2}$ . This means that an execution of  $T_{1+2}$  can only start if on each input channel an event is available. But actually, the code that belongs to  $T_1$  does not depend on the input channels of  $T_2$  and thus could be executed without  $c_4$ . Hence, we obviously change the activation dependencies and delays implicitly by doing such an operation. Thus, we cannot represent and keep the

previous semantics after the merging operation due to missing expressiveness in the formalism. The problem becomes even worse if we consider more complex activation patterns with several activation ports. An internal state transition system within a node offers the possibility to express the original semantics without doing implicit changes to activation dependencies or delays.