# Fakultät II Department für Informatik Abteilung Eingebettete Hardware-/Software-Systeme

## Application Mapping and Communication Synthesis for Object-Oriented Platform-Based Design

Dissertation

zur Erlangung des

Doktorgrades der Naturwissenschaften

(Doctor rerum naturalium)

vorgelegt von

Kim Grüttner

geboren am 06.03.1979 in Delmenhorst

Submitted: January 22, 2015

Advisor: Prof. Dr.-Ing. Wolfgang Nebel First Reader: Prof. Dr. Achim Rettberg Second Reader: Prof. Dr. Rainer Dömer

Defended: March 6, 2015

#### Abstract

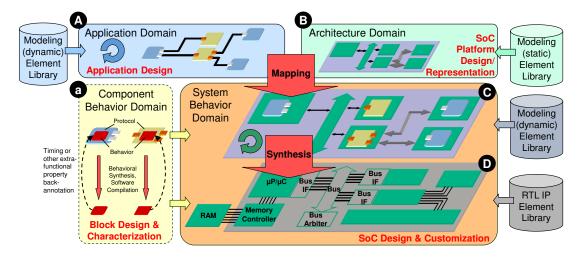

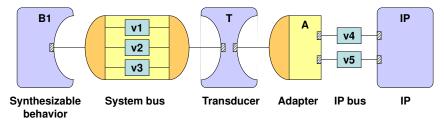

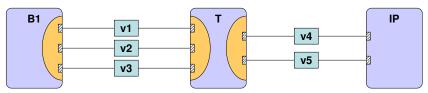

Platform-based design of embedded systems on a chip consists of the parallel functional application specification, configuration of the hardware platform (i.e. connection of processing, memory and physical communication channels) and mapping of the application description on the processing, memory and communication resources of the hardware platform. The main contribution of this work is the seamless object-oriented modeling and automatic refinement of communication. In the application model, communication is specified by method calls on communication objects, independent from a physical communication channel. By means of mapping rules, these application model method calls are automatically transformed (synthesized) and implemented on the processing, memory and communication resources of the hardware platform. This approach enables the exploration and assessment of the impact of different platform configurations and mapping rules on functional and extra-functional properties.

**Keywords:** Embedded system on a chip, object-oriented communication, synthesis, remote method invocation, platform-based design

#### Kurzzusammenfassung

Der plattformbasierte Entwurf eingebetteter Ein-Chip-Systeme, besteht in der parallelen funktionalen Spezifikation der Applikation, Konfiguration der Hardwareplattform (d.h. Verbindung von Berechnungs- und Speicherelementen über physikalische Kommunikationskanäle), und der Abbildung der Applikationsbeschreibung auf die Berechnungs-, Speicher- und Kommunikationsressourcen der Hardwareplattform. Der Hauptbeitrag dieser Arbeit ist die durchgängige objektorientierte Modellierung und automatischen Verfeinerung der Kommunikation. Diese wird im Applikationsmodell mit Hilfe von Methodenaufrufen kommunizierender Objekte, unabhängig von einem physikalischen Übertragungskanal, modelliert. Mit Hilfe einer Abbildungsvorschrift werden diese Methodenaufrufe durch eine automatische Transformation (Synthese) auf Hardwareressourcen, Speicher und Kommunikationsleitungen der Hardwareplattform abgebildet. Dieses Verfahren ermöglicht eine Untersuchung und Bewertung unterschiedlicher Plattformkonfigurationen und Abbildungsvorschriften in Bezug auf funktionale und extra-funktionale Eigenschaften.

Schlagwörter: Eingebettetes Ein-Chip-System, objektorientierte Kommunikation, Synthese, Aufruf entfernter Methoden, plattformbasierter Entwurf

| 1 | Intro | troduction                                         |    |  |  |  |  |  |

|---|-------|----------------------------------------------------|----|--|--|--|--|--|

|   | 1.1   | 1.1 Embedded Systems on a Chip                     |    |  |  |  |  |  |

|   | 1.2   | Design Challenges                                  | 15 |  |  |  |  |  |

|   | 1.3   | Contributions                                      | 17 |  |  |  |  |  |

|   | 1.4   | Basic Idea                                         |    |  |  |  |  |  |

|   | 1.5   | Outline                                            |    |  |  |  |  |  |

| 2 | Goa   | als of the Methodology                             | 25 |  |  |  |  |  |

|   | 2.1   | Introduction                                       | 25 |  |  |  |  |  |

|   | 2.2   | Embedded Systems on a Chip (SoC)                   | 25 |  |  |  |  |  |

|   |       | 2.2.1 IP components                                | 26 |  |  |  |  |  |

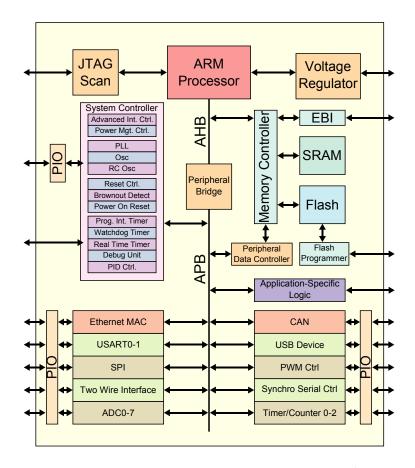

|   |       | 2.2.2 Software Processors                          | 26 |  |  |  |  |  |

|   |       | 2.2.3 Dedicated Hardware                           | 27 |  |  |  |  |  |

|   |       | 2.2.4 Memory                                       | 28 |  |  |  |  |  |

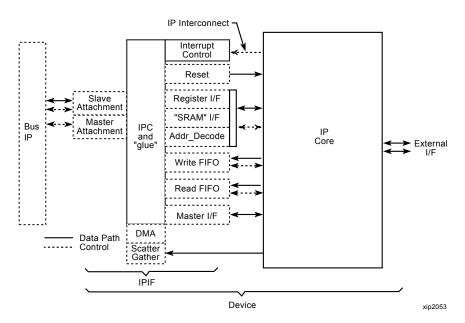

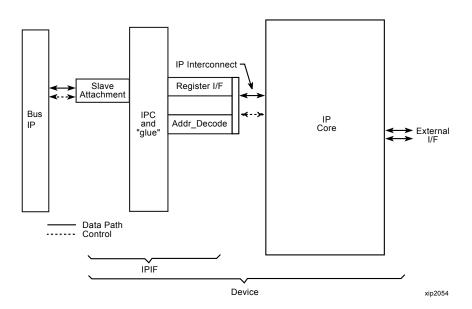

|   |       | 2.2.5 Communication Interfaces                     | 28 |  |  |  |  |  |

|   |       | 2.2.6 Communication Networks                       | 29 |  |  |  |  |  |

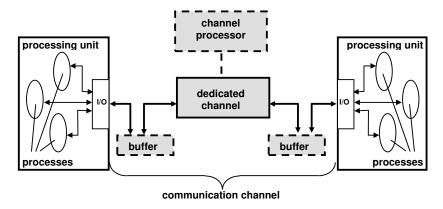

|   |       | 2.2.6.1 Point-To-Point Communication               | 29 |  |  |  |  |  |

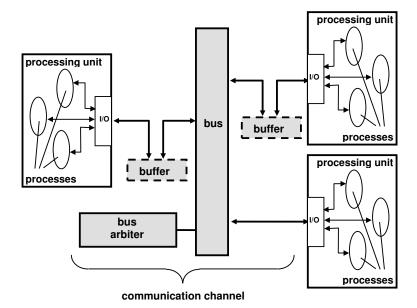

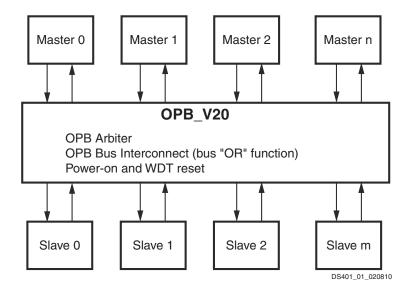

|   |       | 2.2.6.2 Bus Communication                          | 29 |  |  |  |  |  |

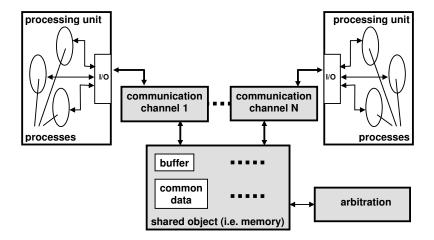

|   |       | 2.2.6.3 Shared Object Communication                | 30 |  |  |  |  |  |

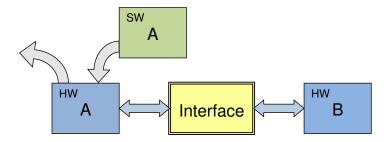

|   |       | 2.2.7 Application mapping                          | 31 |  |  |  |  |  |

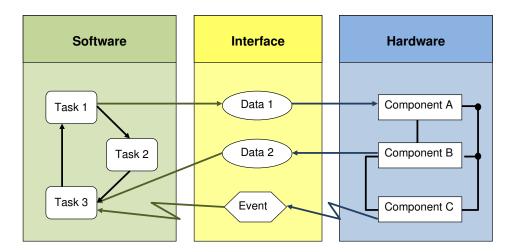

|   | 2.3   | Communication in Embedded System                   | 31 |  |  |  |  |  |

|   |       | 2.3.1 Structural inter-component access techniques | 32 |  |  |  |  |  |

|   |       | 2.3.1.1 Memory mapped I/O                          | 32 |  |  |  |  |  |

|   |       | 2.3.1.2 Port I/O                                   | 33 |  |  |  |  |  |

|   |       | 2.3.2 Behavioral inter-component access techniques | 33 |  |  |  |  |  |

|   |       | 2.3.2.1 Polling                                    | 33 |  |  |  |  |  |

|   |       | 2.3.2.2 Interrupts                                 | 33 |  |  |  |  |  |

|   |       | 2.3.2.3 DMA                                        | 34 |  |  |  |  |  |

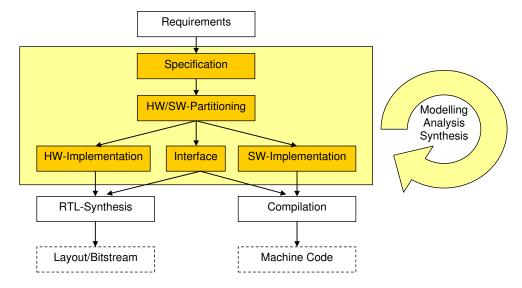

|   | 2.4   | Requirements on Communication-Centric Design       | 35 |  |  |  |  |  |

|   |       | 2.4.1 Modeling                                     | 36 |  |  |  |  |  |

|   |       | 2.4.2 Analysis                                     | 37 |  |  |  |  |  |

|   |       | 2.4.3 Synthesis                                    | 37 |  |  |  |  |  |

|   |       | 2.4.4 Implicit Requirements and Consequences       | 38 |  |  |  |  |  |

|   | 2.5   | Summary                                            |    |  |  |  |  |  |

| 3 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                                                                                                                                                                                                                                                                |                                                                                                                |

|---|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|   | 3.1         | Introduct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ion                                                                                                                                                                                                                                                              | 41                                                                                                             |

|   | 3.2         | Selected 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Mathematical Notations                                                                                                                                                                                                                                           | 41                                                                                                             |

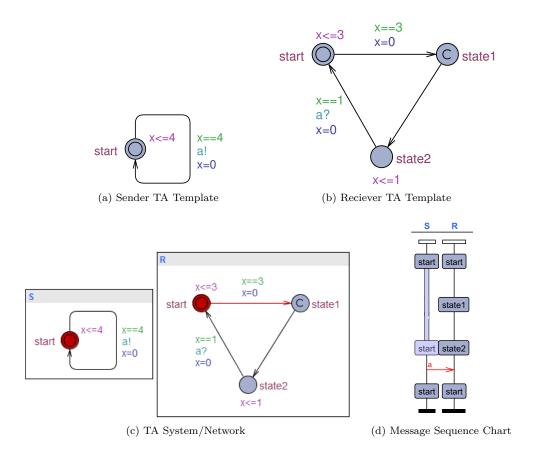

|   | 3.3         | Timed A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | itomata                                                                                                                                                                                                                                                          | 43                                                                                                             |

|   |             | 3.3.1 De                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | finition                                                                                                                                                                                                                                                         | 43                                                                                                             |

|   |             | 3.3.2 G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | aphical notation in Uppaal                                                                                                                                                                                                                                       | 44                                                                                                             |

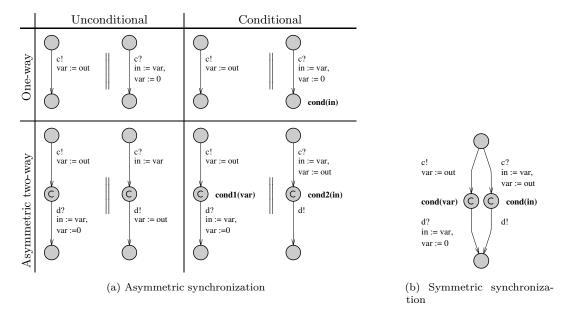

|   |             | 3.3.3 Sy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nchronous Value Passing                                                                                                                                                                                                                                          | 45                                                                                                             |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                  | 46                                                                                                             |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                | 46                                                                                                             |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                  | 47                                                                                                             |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | v 1                                                                                                                                                                                                                                                              | $\frac{1}{47}$                                                                                                 |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                  | 47                                                                                                             |

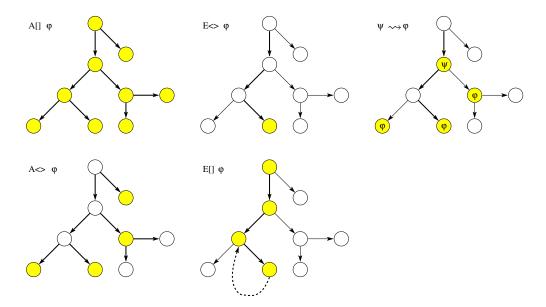

|   | 3.4         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                  | 48                                                                                                             |

|   | 9.1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                  | 48                                                                                                             |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                  | 50                                                                                                             |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                  | 52                                                                                                             |

|   |             | 0.4.0 M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | odel of Denfermance (MoD)                                                                                                                                                                                                                                        | 52<br>53                                                                                                       |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                  |                                                                                                                |

|   | 0.5         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | v                                                                                                                                                                                                                                                                | 55                                                                                                             |

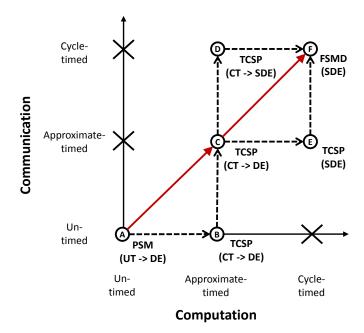

|   | 3.5         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | G(                                                                                                                                                                                                                                                               | 57                                                                                                             |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                | 59                                                                                                             |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                  | 59                                                                                                             |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                  | 60                                                                                                             |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | v                                                                                                                                                                                                                                                                | 60                                                                                                             |

|   | 3.6         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                  | 61                                                                                                             |

|   |             | 3.6.1 La                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nguage                                                                                                                                                                                                                                                           | 61                                                                                                             |

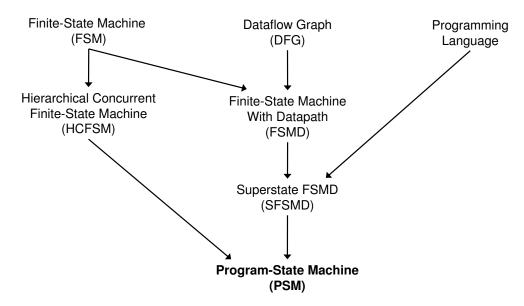

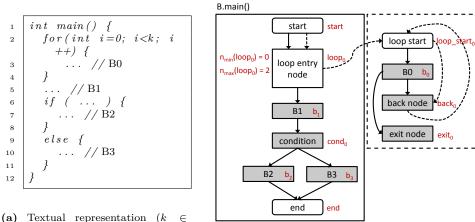

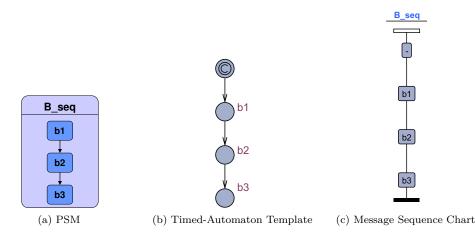

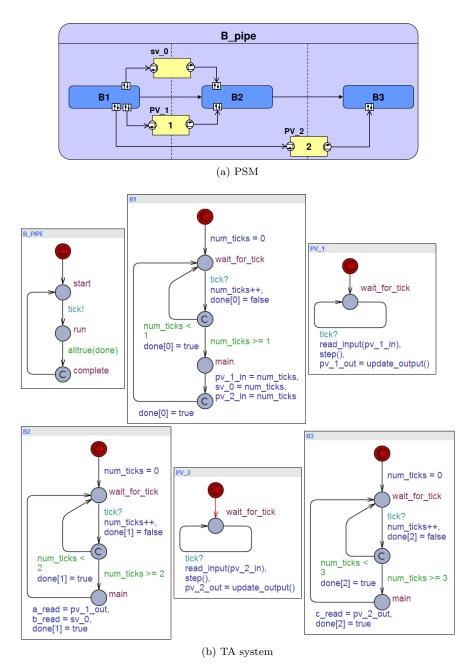

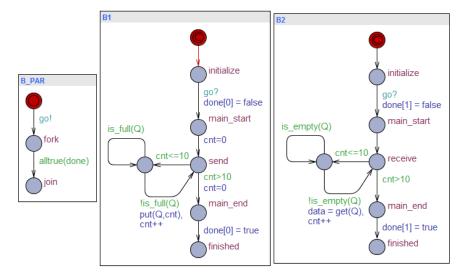

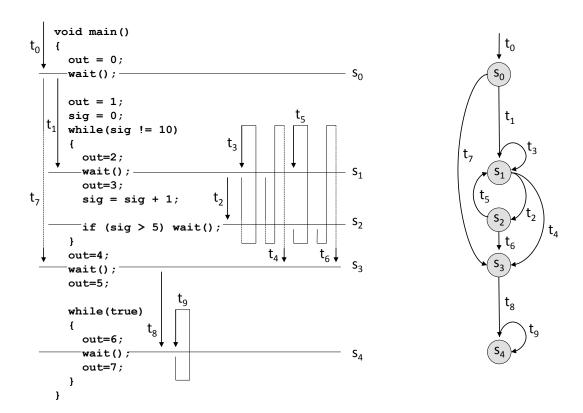

|   |             | 3.6.2 Pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ogram State Machines                                                                                                                                                                                                                                             | 63                                                                                                             |

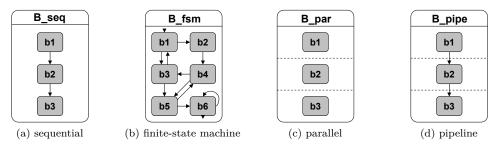

|   |             | 3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5.2.1 Program-States                                                                                                                                                                                                                                             | 63                                                                                                             |

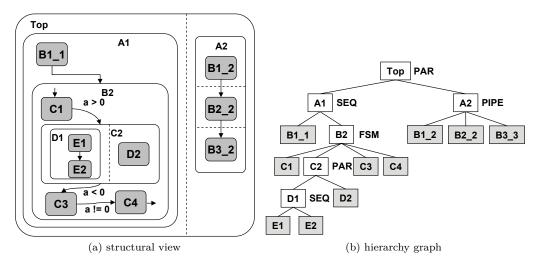

|   |             | 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.2.2 Hierarchical composition                                                                                                                                                                                                                                   | 65                                                                                                             |